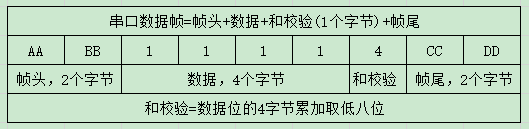

基于FPGA的串口指令帧接收与解析的verilog代码 网上的verilog串口指令帧接收与解析源码很多,但大多数都说不到点子上,对初学者来说很不友好,今天分享一个自己调通的小工程。 串口指令帧格式如下:  串口接收模块直接用的正点原子的源码,个人感觉正点原子的代码虽然写得冗杂,但严谨性还行,数据在波特率计数周期的中间点采集,源码如下:

串口接收模块直接用的正点原子的源码,个人感觉正点原子的代码虽然写得冗杂,但严谨性还行,数据在波特率计数周期的中间点采集,源码如下:

module uart_recv(

input sys_clk, //系统时钟

input sys_rst_n, //系统复位,低电平有效

(*mark_debug ="true"*) input uart_rxd, //UART接收端口

(*mark_debug ="true"*) output reg uart_done, //接收一帧数据完成标志信号

(*mark_debug ="true"*) output reg [7:0] uart_data //接收的数据

);

//parameter define

parameter CLK_FREQ = 100_000_000; //系统时钟频率

parameter UART_BPS = 230400; //串口波特率

localparam BPS_CNT = CLK_FREQ/UART_BPS; //为得到指定波特率,

//需要对系统时钟计数BPS_CNT次

//reg define

reg uart_rxd_d0;

reg uart_rxd_d1;

reg [15:0] clk_cnt; //系统时钟计数器

reg [ 3:0] rx_cnt; //接收数据计数器

reg rx_flag; //接收过程标志信号

reg [ 7:0] rxdata; //接收数据寄存器

//wire define

wire start_flag;

//*****************************************************

//** main code

//*****************************************************

//捕获接收端口下降沿(起始位),得到一个时钟周期的脉冲信号

assign start_flag = uart_rxd_d1 & (~uart_rxd_d0);

//对UART接收端口的数据延迟两个时钟周期

always @(posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n) begin

uart_rxd_d0

关注

打赏

热门博文

- FPGA解码SDI视频,GTX加官方IP解码方案,代码逐行讲解,提供验证过的工程源码,可直接移植

- FPGA采集OV5640摄像头HDMI输出,代码逐行讲解,提供验证过的工程源码,可直接拿去用

- FPGA的GTP视频传输方案,提供HDMI和OV5640摄像头两种例程

- FPFA光通信GTP眼图测试ibert,细节很多

- 浅谈FPGA网络PHY芯片RTL8211FD的配置和简单使用

- 基于FPGA的图像去雾算法实现,附带工程源码

- FPGA运动目标检测,基于米联客FDMA设计开发,A7和zynq两个版本

- FPGA图像三帧缓存,手写米联客FDMA3.0控制器,逐行讲解代码

- 基于ZYNQ7100的AD7606电压实时监测系统,过压蜂鸣器报警

- FPGA的HDMI字符显示,图像采集叠加时钟显示