前言

亚稳态这个问题经常出现在面试中,因此,需要把标题上那一键三问全部搞清楚

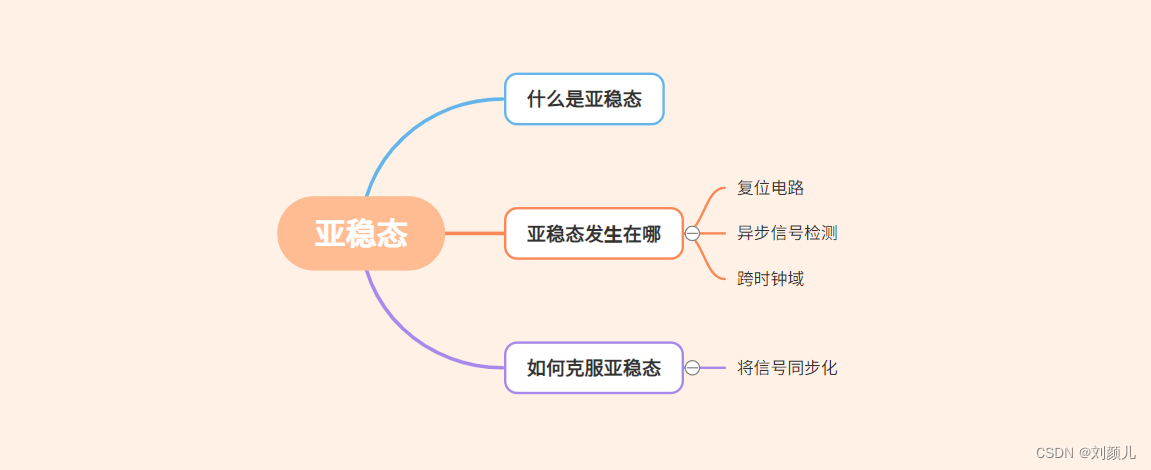

正文看了好几位前辈对亚稳态的解释,我再结合自己的理解,整理一份关于亚稳态的笔记,下面是内容纲要

亚稳态主要是指触发器的输出在一段时间(决断时间:resolution time)内不能达到一个确定的状态,过了这段时间触发器的输出随机选择输出0/1

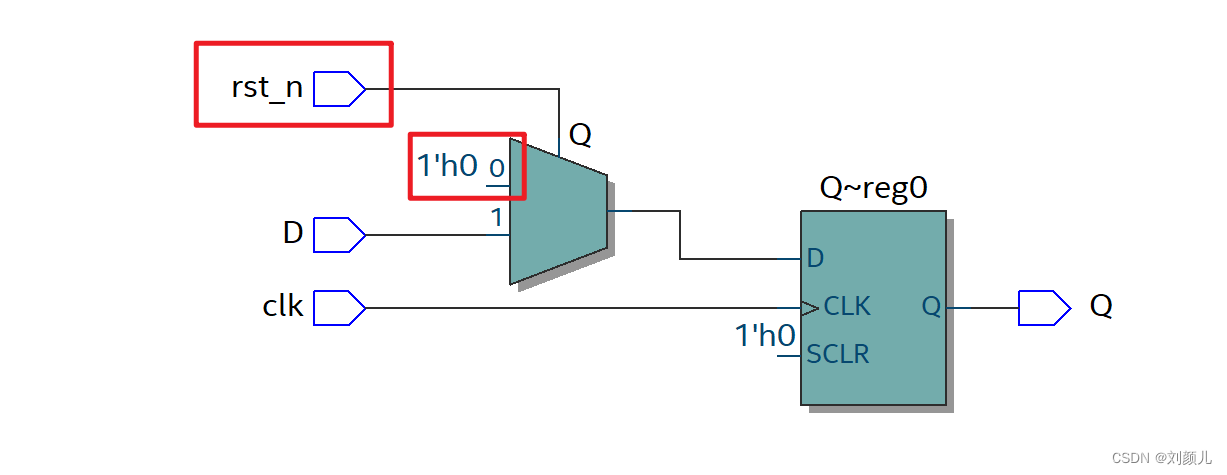

复位电路分为同步复位、异步复位,分别对其进行仿真说明 首先要明确什么是异步、同步? 异步,同步是指输出信号边沿是否和clk上升沿对齐,对齐即为同步,没有对齐即为异步 注:不是看复位信号和clk是否对齐,而是看输出信号和clk是否对齐

always块中的敏感信号为:always @(posedge clk) 由综合出的电路可知,当rst_n=0时,Q=1'h0

module ff(

input clk,

input rst_n,

input D,

output reg Q

);

always @(posedge clk) begin

if(!rst_n)

Q

关注

打赏