前言

一听到流水线,我就想到工厂中流水线上的工人,只需要重复做一样工作即可

等以后退休了,我也想去工厂给饼干扎洞洞哈哈哈

正文目前我看到的使用流水线的场景,大多是用面积换速度的场景

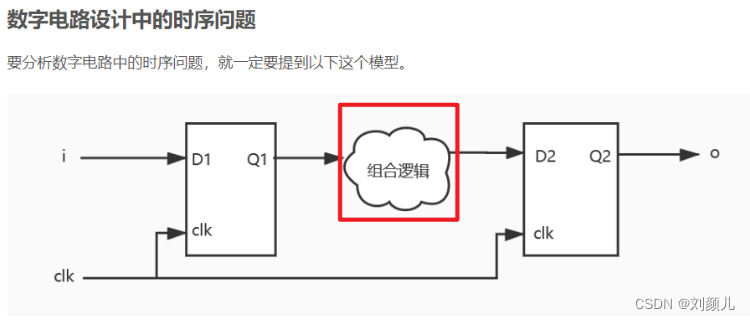

一、什么是流水线流水线技术:一个启动程序指令的并行执行的过程。在原本的组合逻辑中,插入寄存器后,就形成了流水线

由于组合逻辑越长,对时序的影响越大,因此为了有效减小时延,就可以在组合逻辑中加入寄存器,如下

在实现8bit全加器时(流水线实现8bit全加器),使用流水线来同时处理低4位和高4位的运算,这里能使用流水线的原因是,组合逻辑时延大,并且数据流向是单方向的

后面这3个等遇到再补充

2.1.2 功能模块之间功能模块之间的流水线,用乒乓 buffer 来交互数据

2.1.3 I/O 瓶颈 2.1.4 片内 sram 的读操作 2.2 使用流水线后的效果 2.2.1 优点增加了数据吞吐量,从而可以提高时钟频率

关键路径中插入流水线,能够提高系统时钟频率

2.2.1 缺点流水线设计会导致原有通路延时增加:这里是说流水线增加了单个数据的延时,每增加一个寄存器,会增加一个输入到输出的寄存器需要的时间,因此原有通路时延增加;但是着眼于全局,流水线是减小了时延的

功耗增加,面积增加,硬件复杂度增加

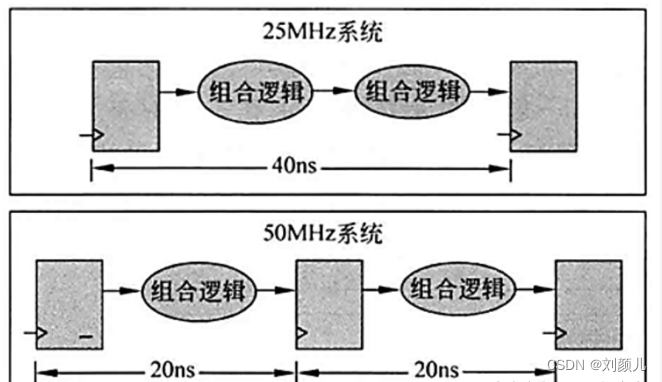

2.3 关键路径、时钟频率关键路径:由非时钟逻辑元件引起的最大延迟,其他路径需要等关键路径执行完成,其他路径才可以继续执行 时钟频率:由2级寄存器之间的时延决定,如下图

牛客 - 流水线试题