前言

例化这个FIFO的IP核用于SDRAM中读写FIFO

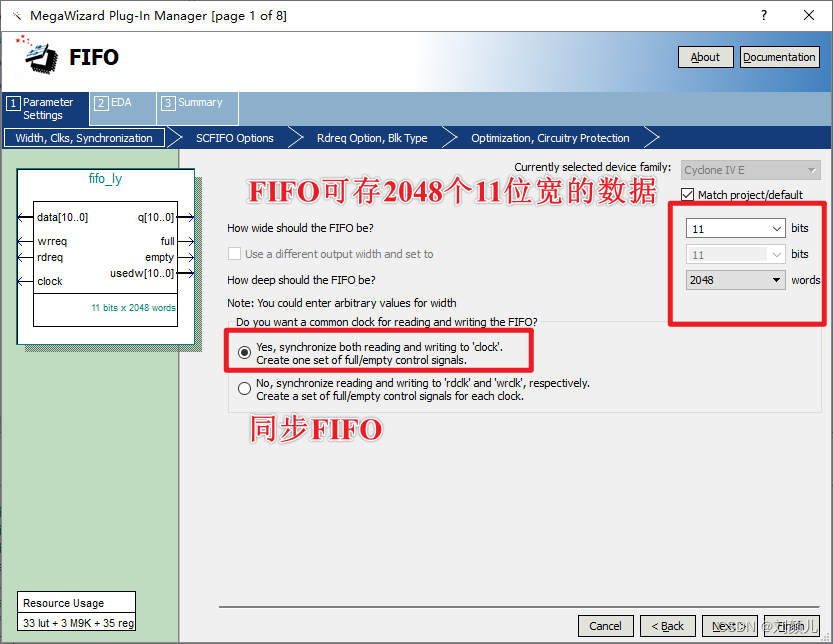

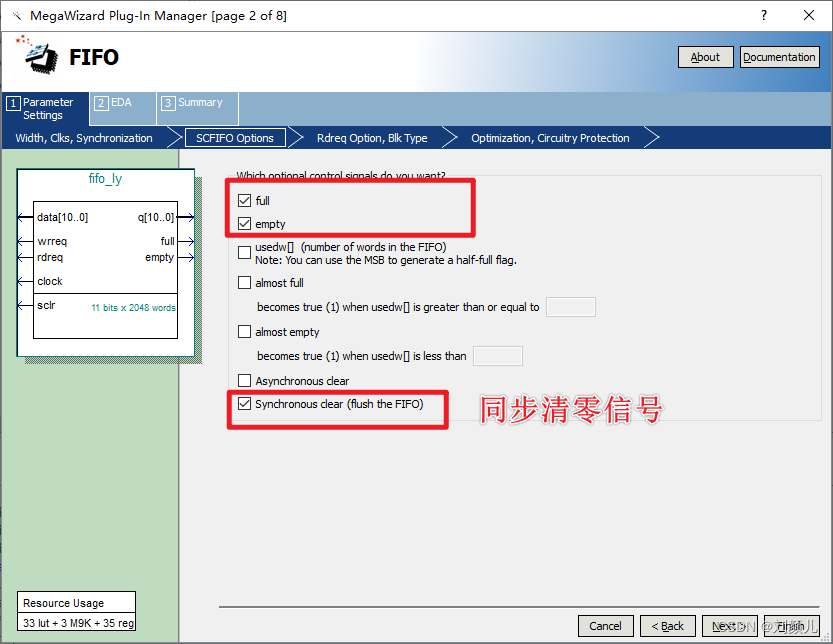

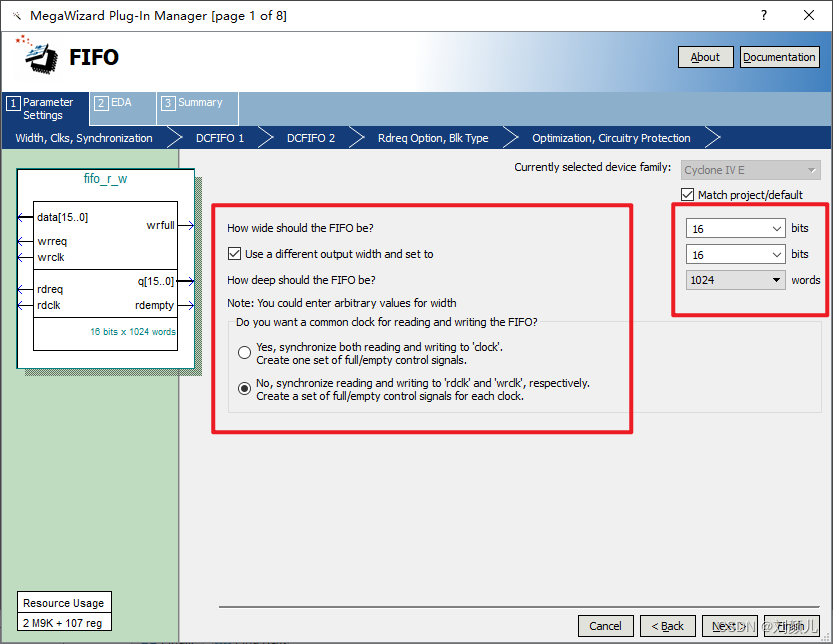

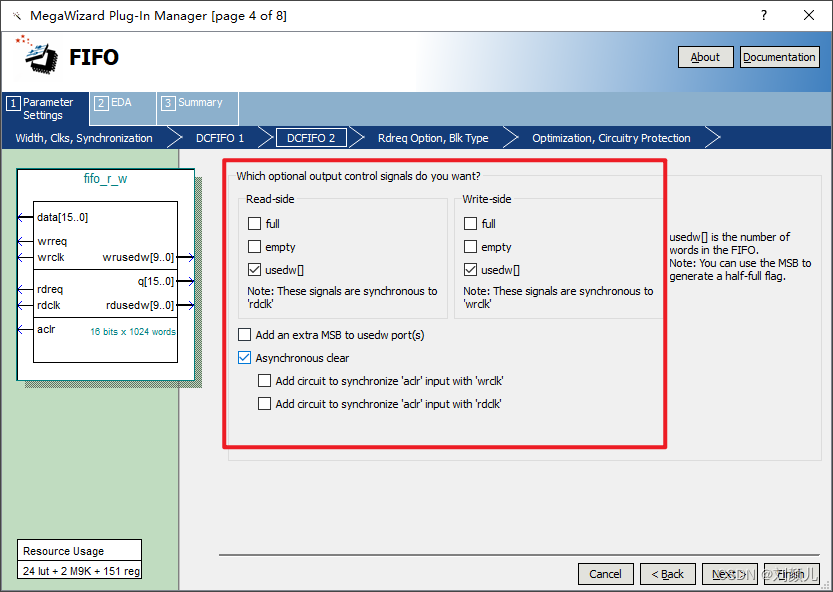

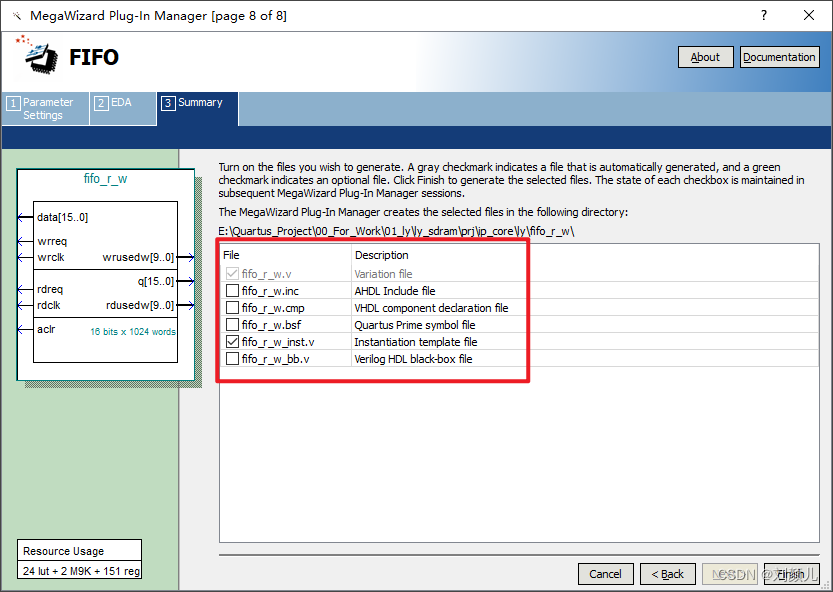

正文 一、异步FIFO只配置了下面3部分,其余保持默认即可 1.选择NO:配置成异步FIFO(如果配置同步FIFO,就选择YES) 2.大小配置成:可以存储1024个16位宽的数据

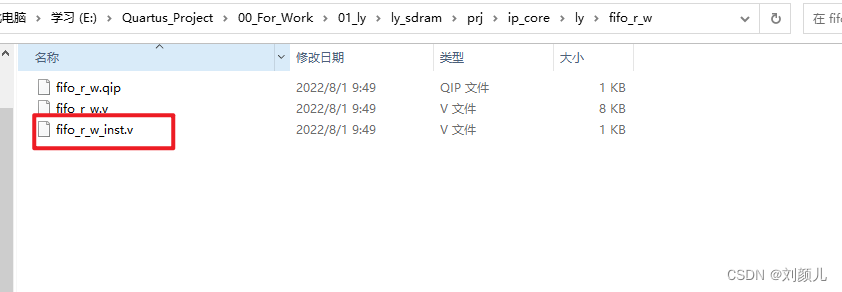

配置完成后,即可到文件夹找到例化文件,将其复制到顶层模块中

//------------- wr_fifo_data -------------

fifo_r_w wr_fifo_data(

//用户接口

.wrclk (wr_fifo_wr_clk ), //写时钟

.wrreq (wr_fifo_wr_req ), //写请求

.data (wr_fifo_wr_data), //写数据

//SDRAM接口

.rdclk (sdram_clk ), //读时钟

.rdreq (sdram_wr_ack ), //读请求

.q (sdram_data_in ), //读数据

.rdusedw (wr_fifo_num ), //FIFO中的数据量

.wrusedw ( ),

.aclr (~sdram_rst_n || wr_fifo_rst) //清零信号

);

//------------- rd_fifo_data -------------

fifo_r_w rd_fifo_data(

//sdram接口

.wrclk (sdram_clk ), //写时钟

.wrreq (sdram_rd_ack ), //写请求

.data (sdram_data_out ), //写数据

//用户接口

.rdclk (rd_fifo_rd_clk ), //读时钟

.rdreq (rd_fifo_rd_req ), //读请求

.q (rd_fifo_rd_data), //读数据

.rdusedw ( ),

.wrusedw (rd_fifo_num ), //FIFO中的数据量

.aclr (~sdram_rst_n || rd_fifo_rst) //清零信号

);