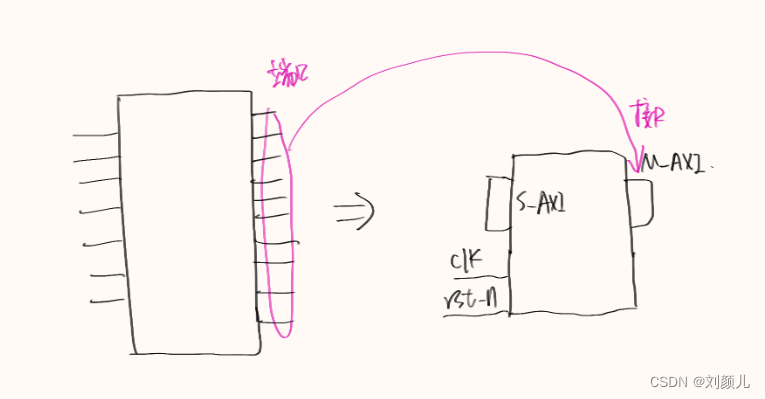

目标:将一个模块封装成带有AXI接口的IP核,方便PL、PS之间数据高速通信

在vivado中的图形化界面,使用赛灵思的官方IP核,就会发现,很多IP核都会用到AXI接口,那什么是接口,为什么要用接口呢? 接口是多个端口合在一起的,这样在连接不同IP核时就可以将多个端口连接,不用再一个一个端口进行连接,这样做的主要目的是为了IP核之间连接方便

软件版本:vivado2020.1 目标:将异步FIFO封装成AXI-stream接口

软件版本:vivado2020.1 目标:将异步FIFO封装成AXI-stream接口

推荐使用第二种方法

一、使用官方IP核

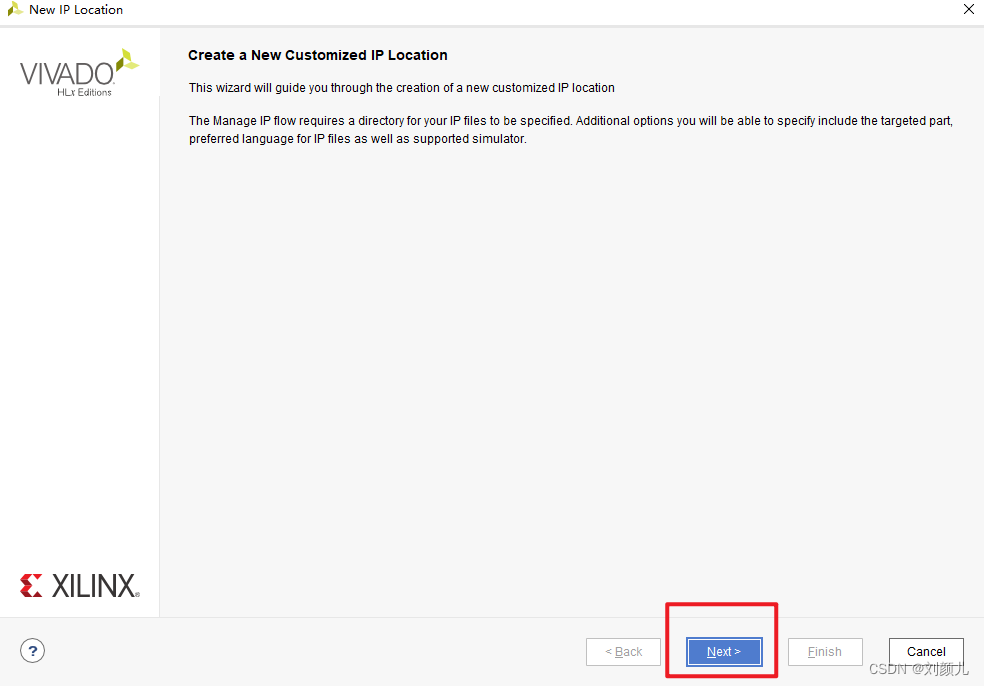

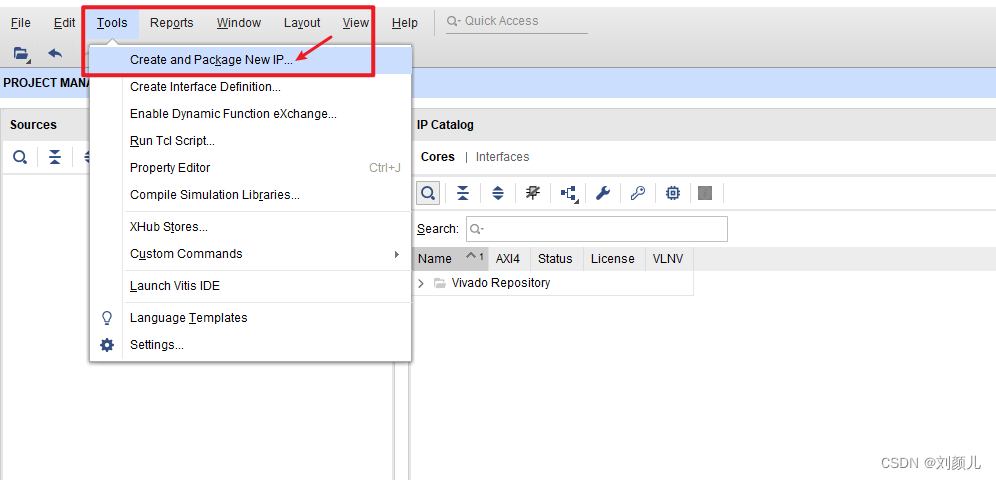

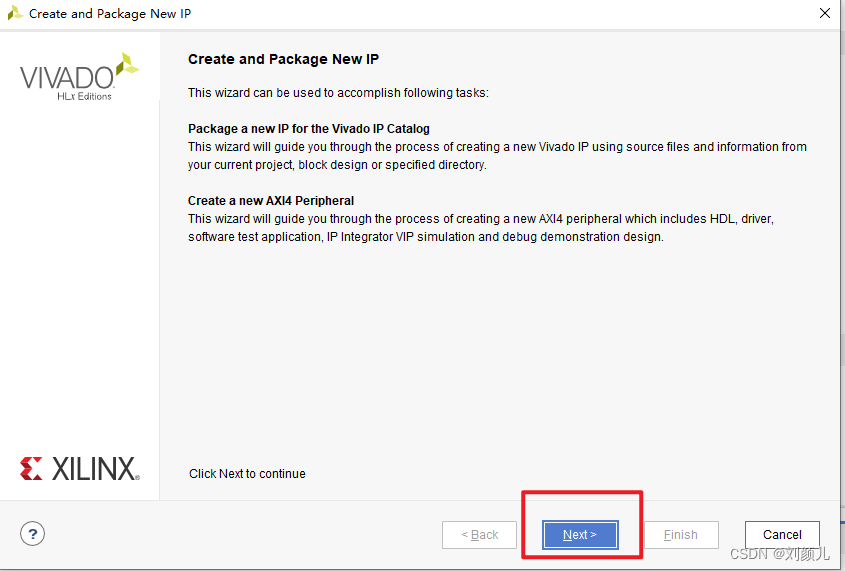

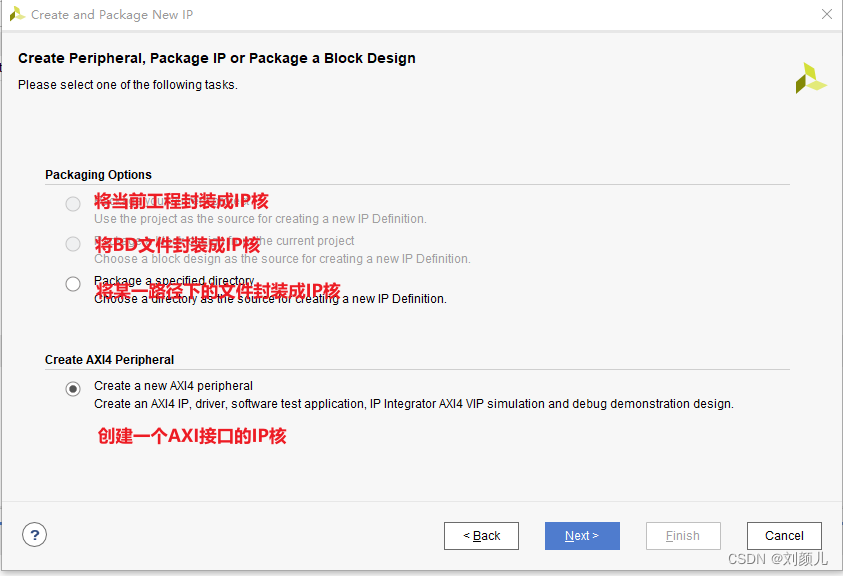

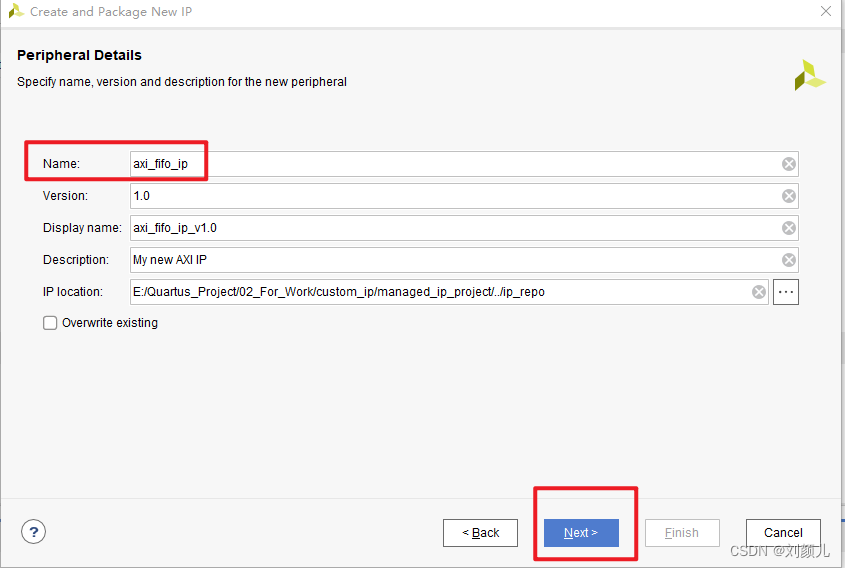

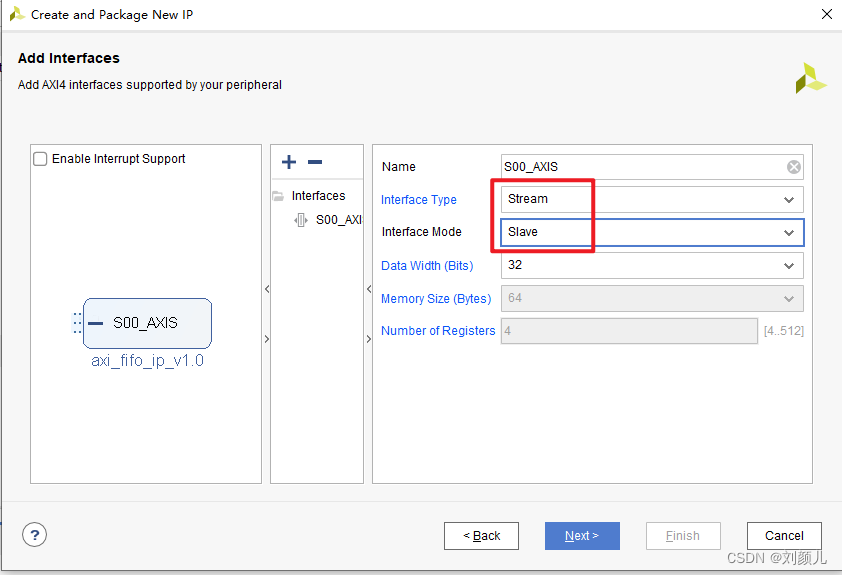

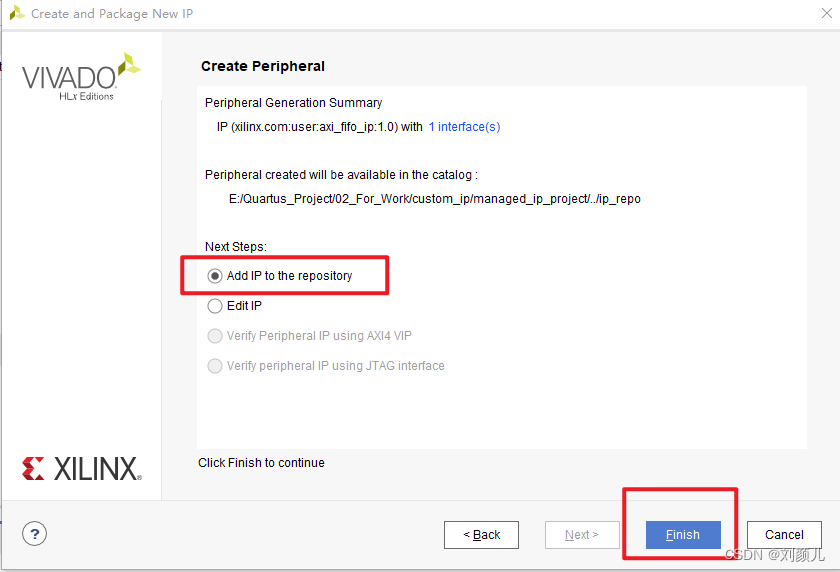

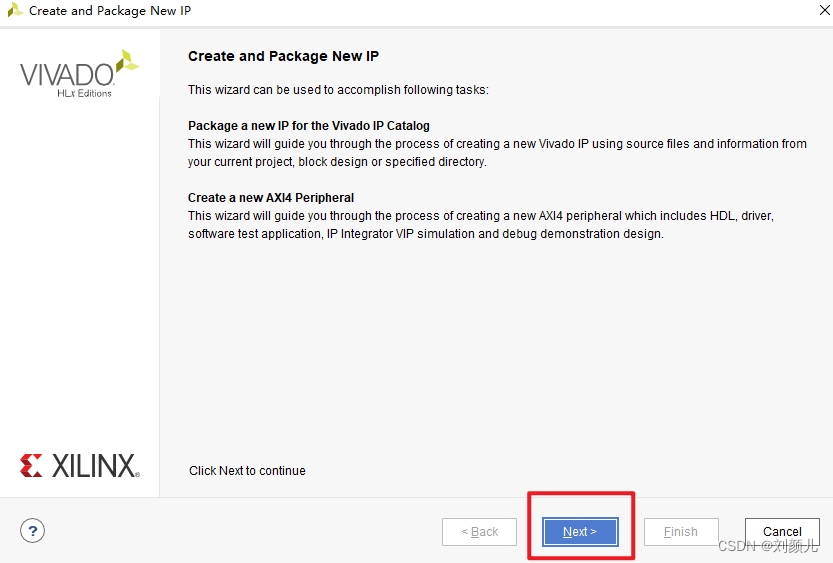

新建自己的IP核

新建自己的IP核

添加IP核到工程里

添加IP核到工程里

然后将自己的代码例化到官方给出的代码中

然后将自己的代码例化到官方给出的代码中

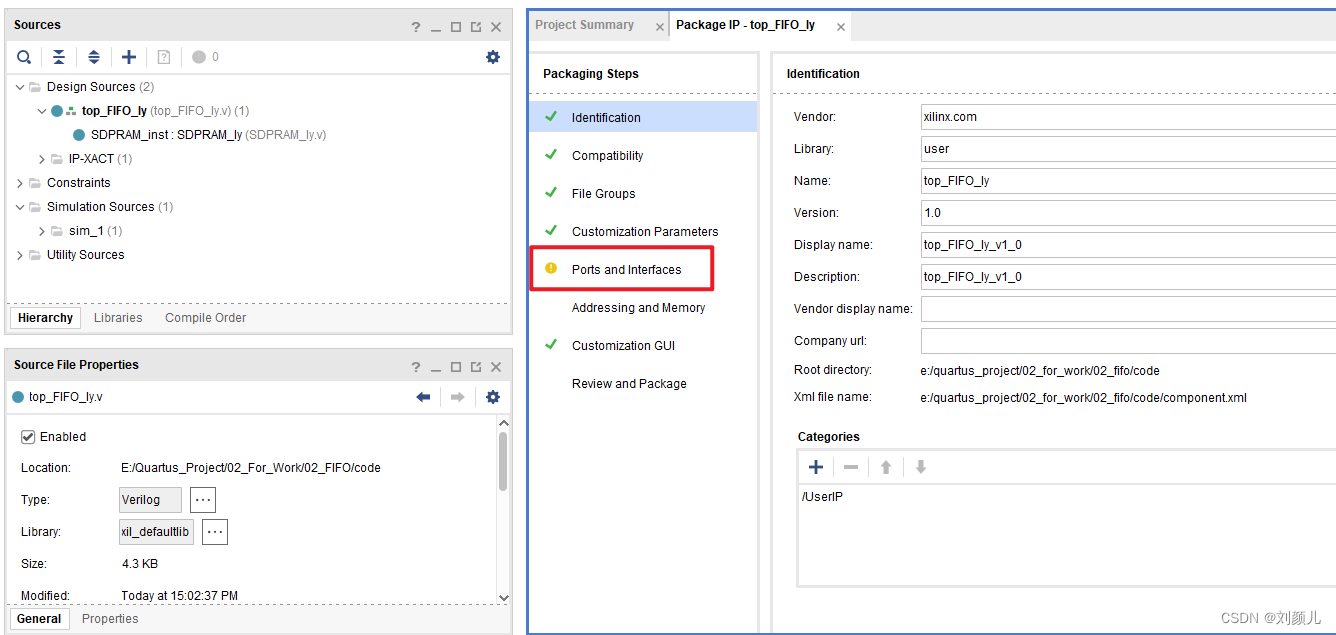

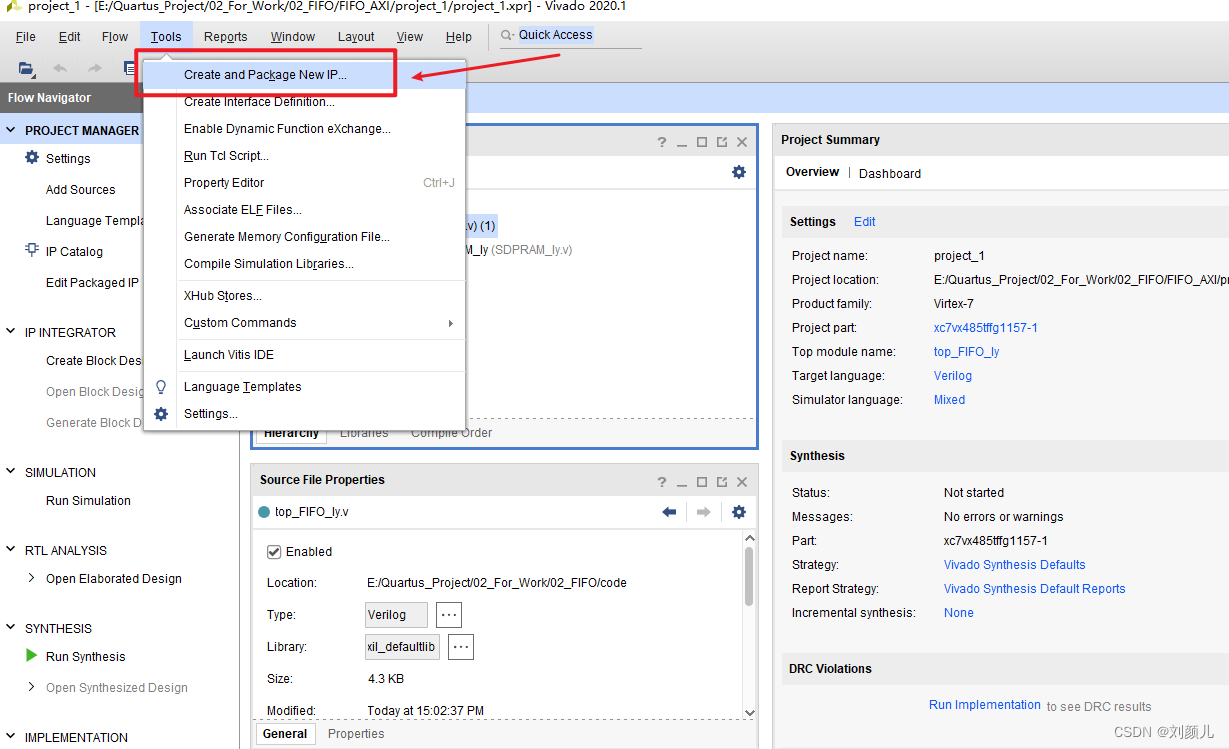

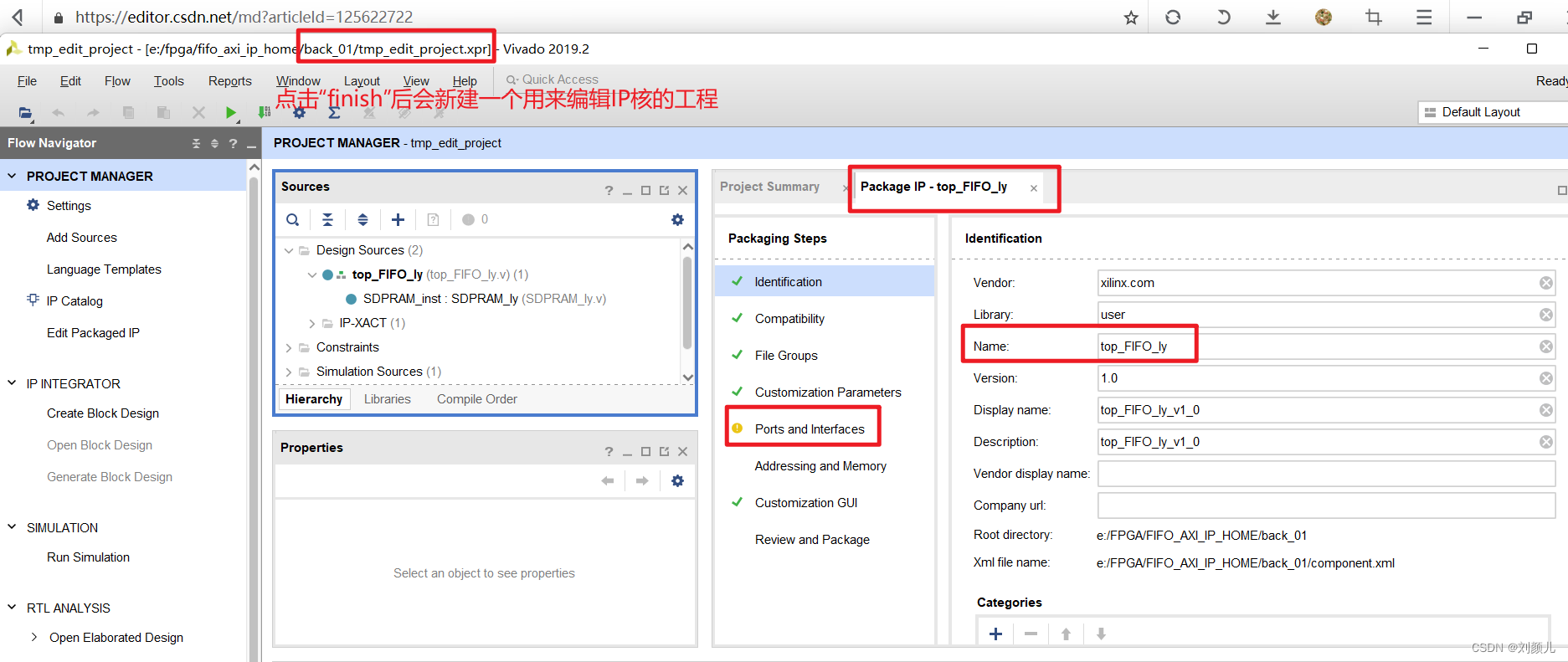

先建立好自己要用来封装IP的工程,在此工程的基础上,将该工程封装成一个IP核,且带有AXI接口 注:有几处的文件命名被我修改过,但是每步的操作是相同的,所以按照步骤即可,命名可以按照自己的来

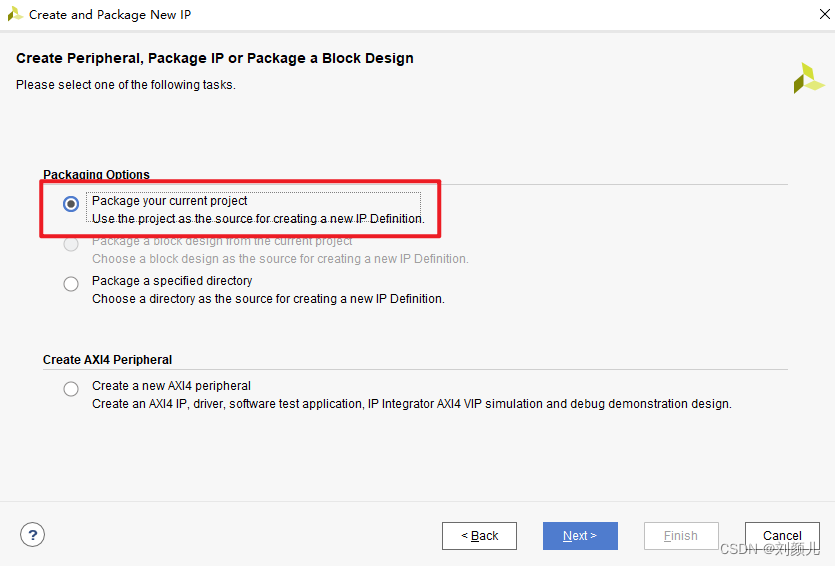

这一步和上一个方法不一样,要选择当前的工程

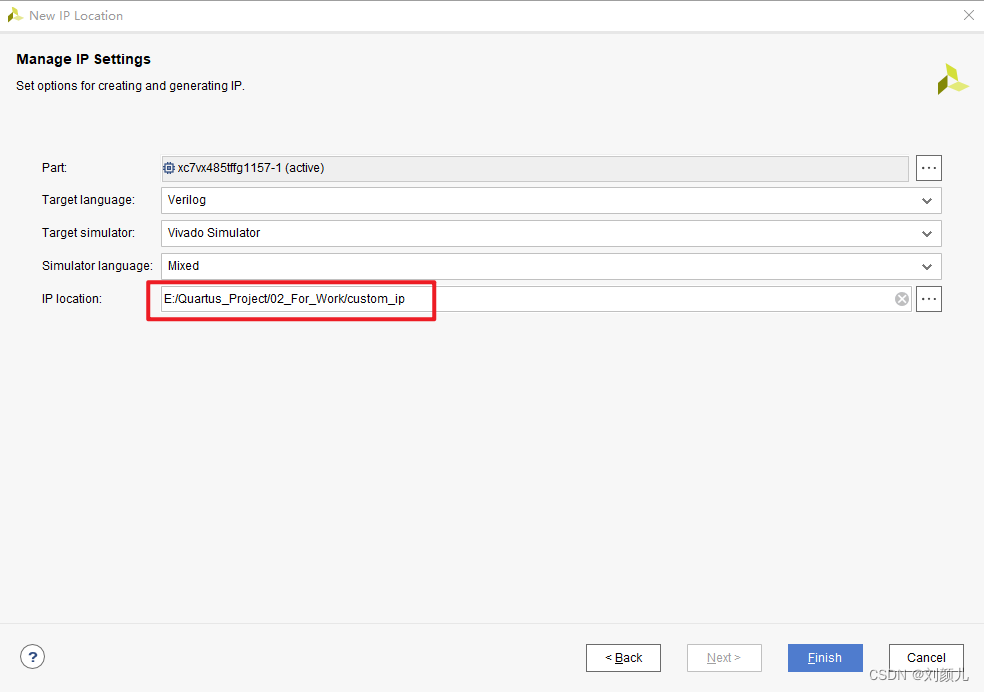

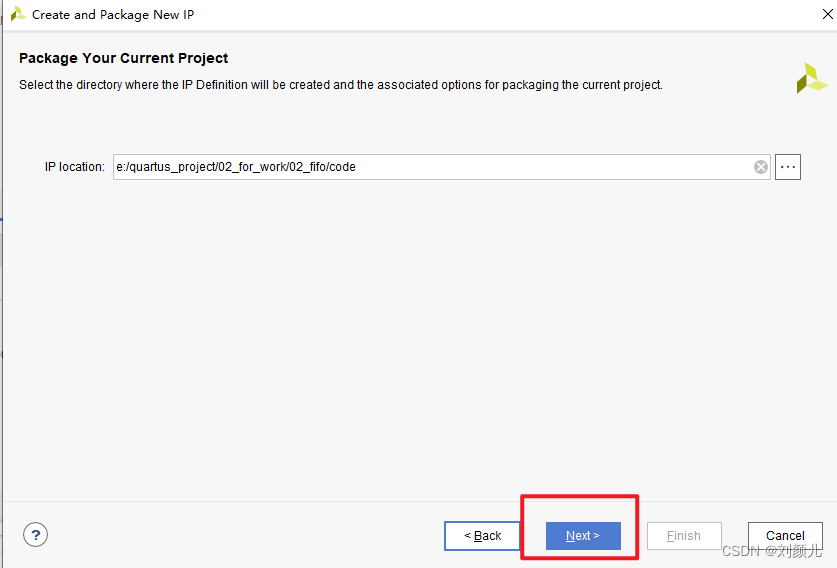

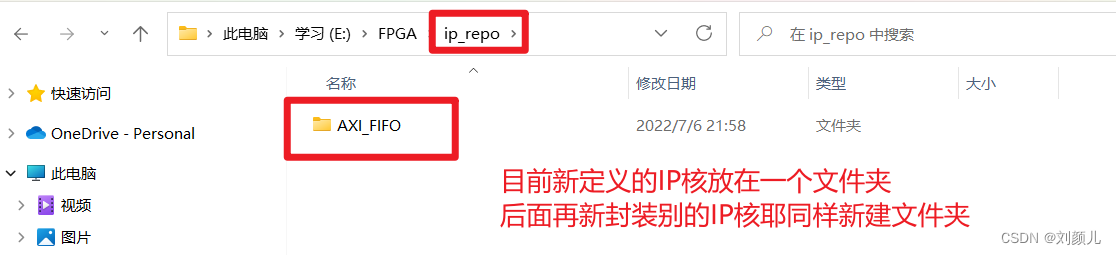

这一步和上一个方法不一样,要选择当前的工程  这里的IP核位置,推荐把你自己封装的所有的IP核都放在同一个文件夹里面

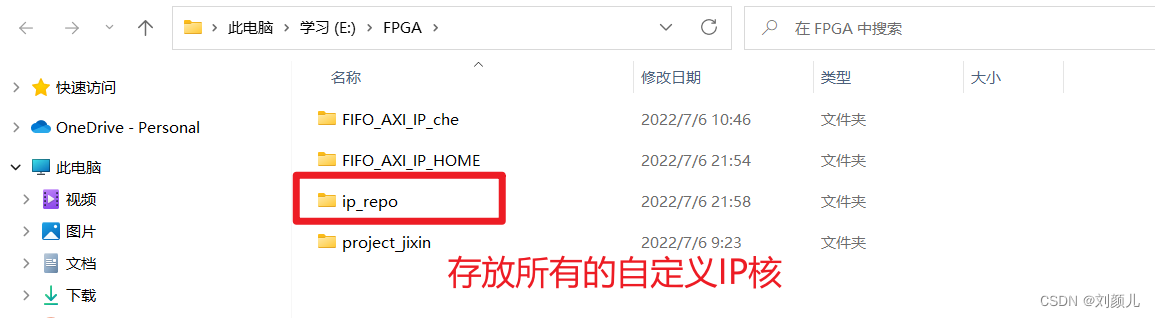

这里的IP核位置,推荐把你自己封装的所有的IP核都放在同一个文件夹里面

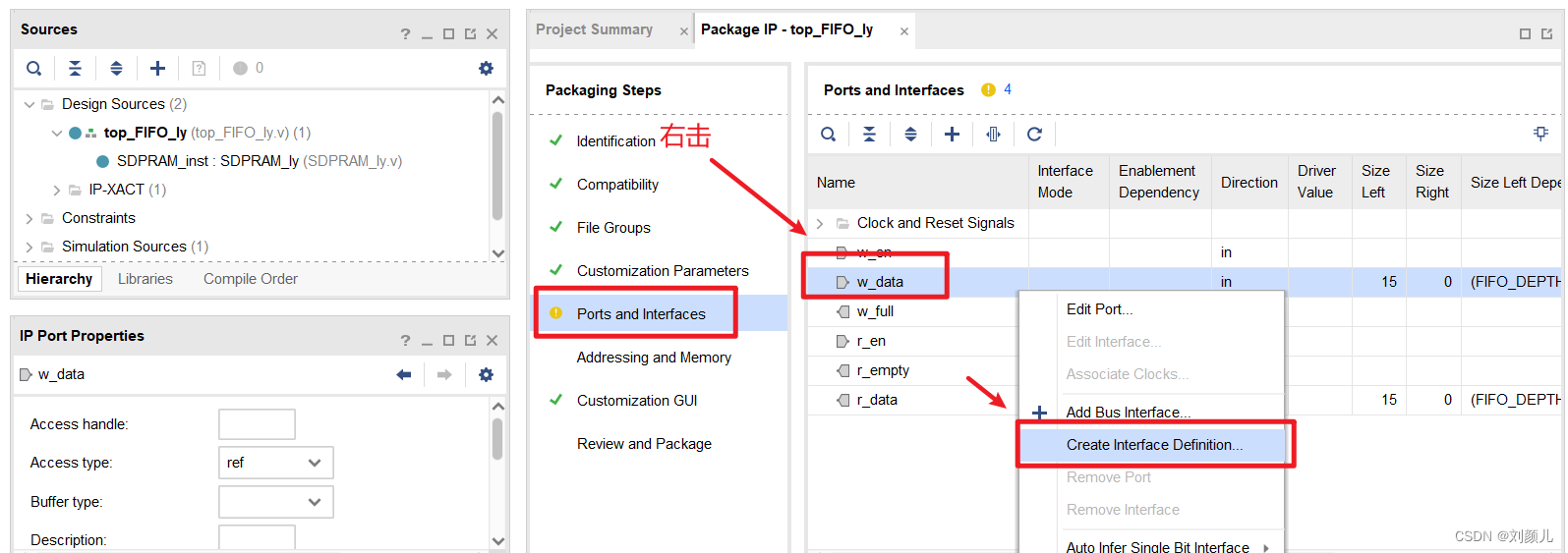

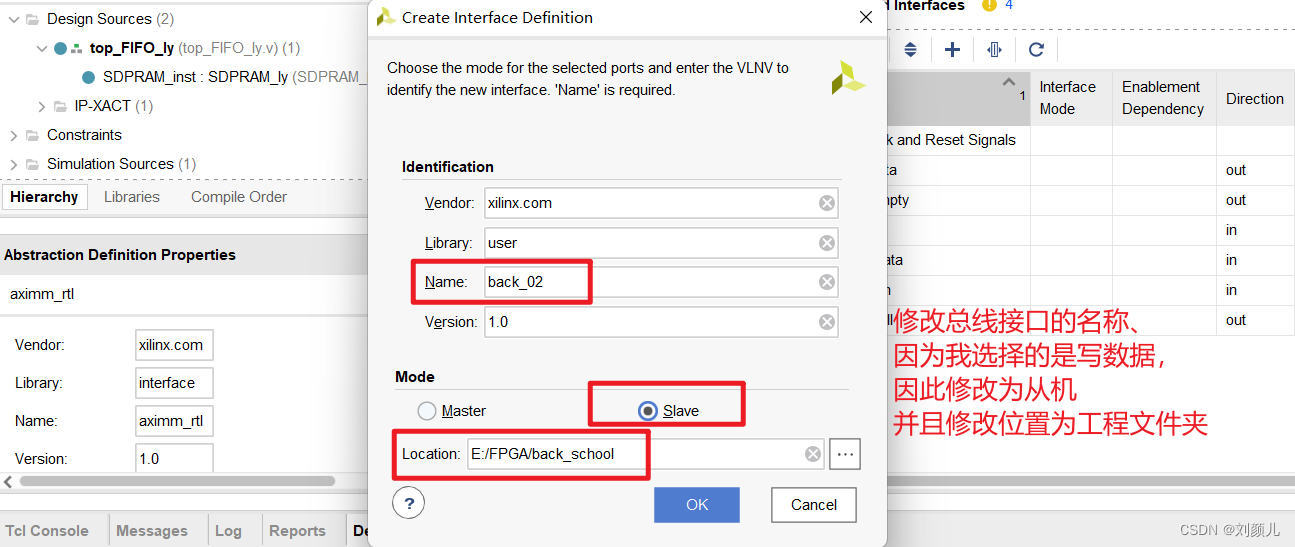

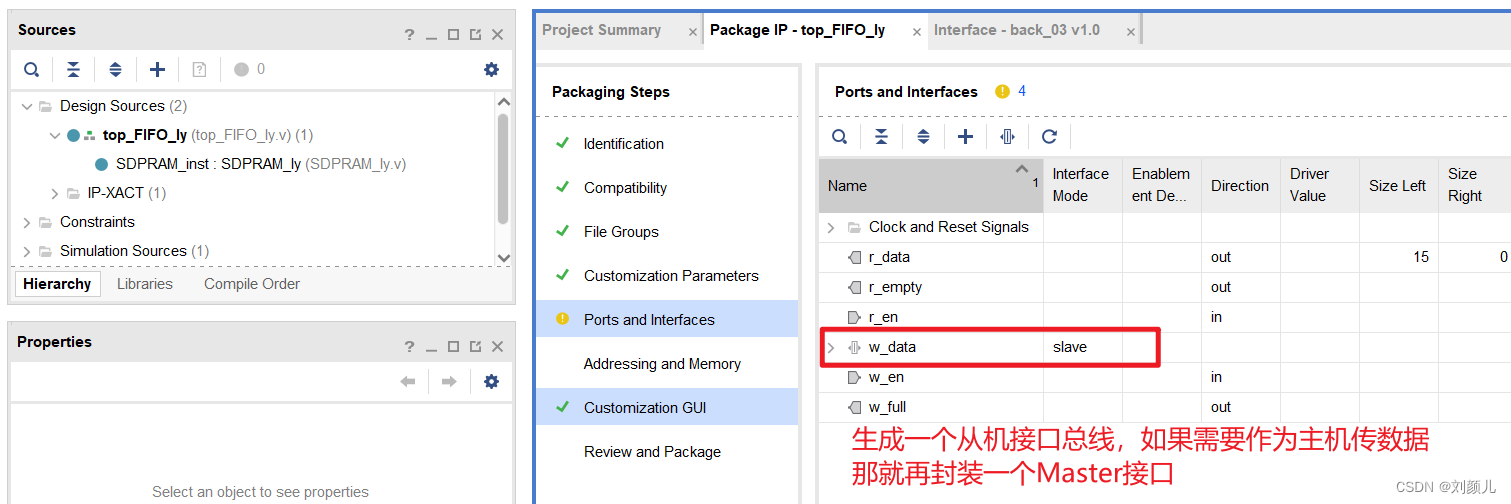

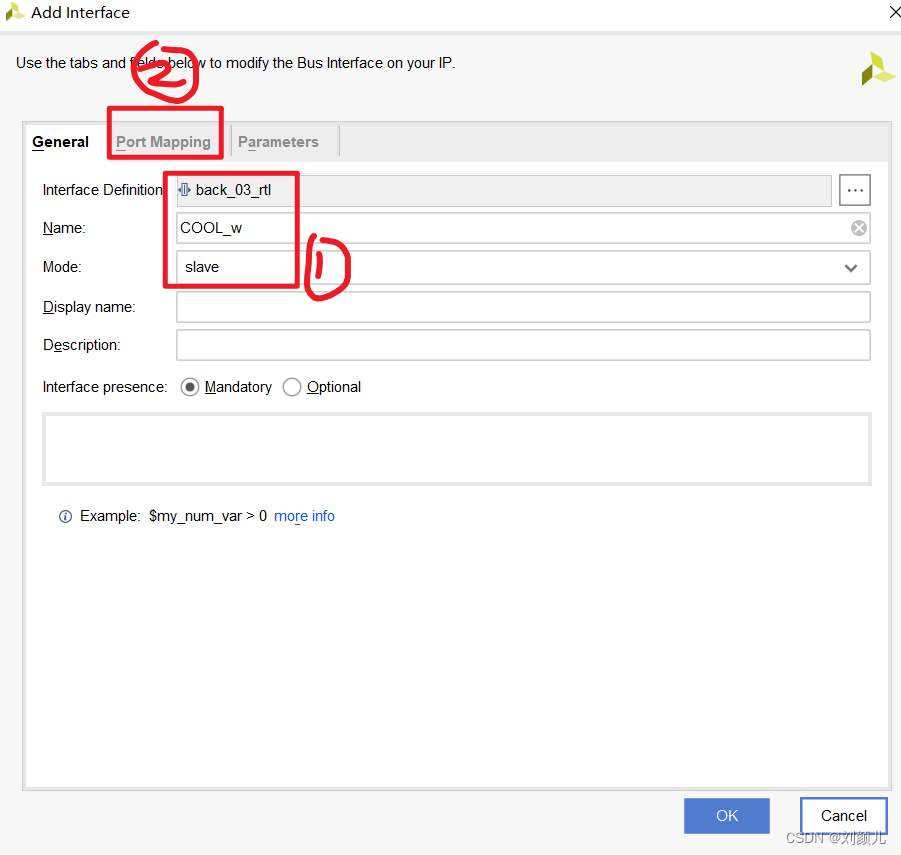

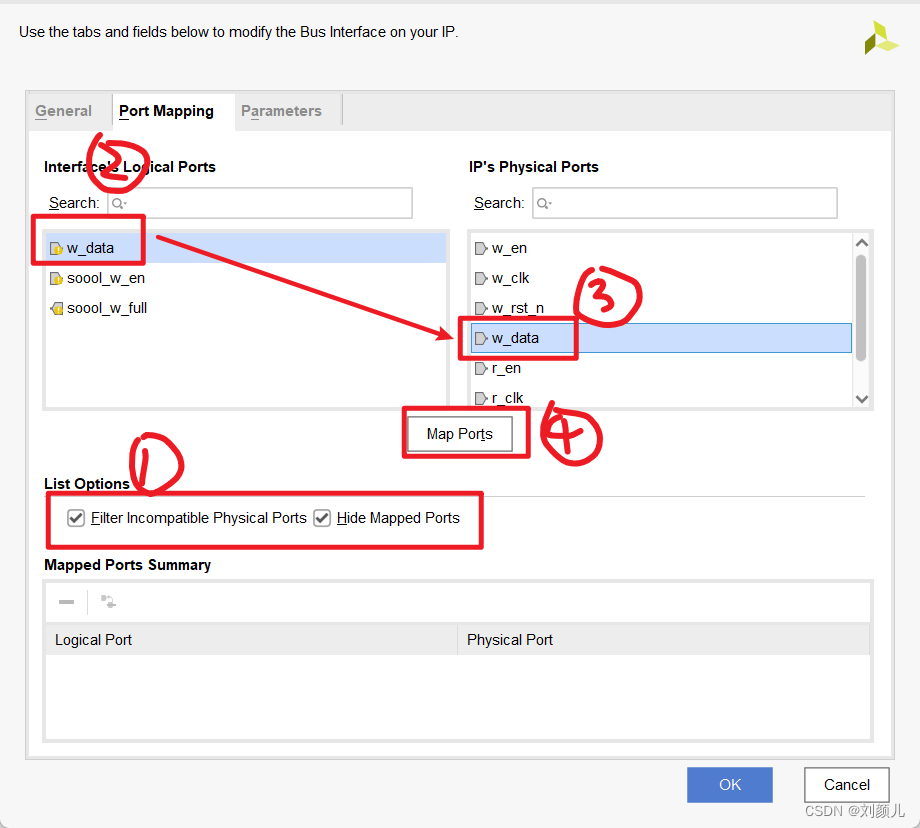

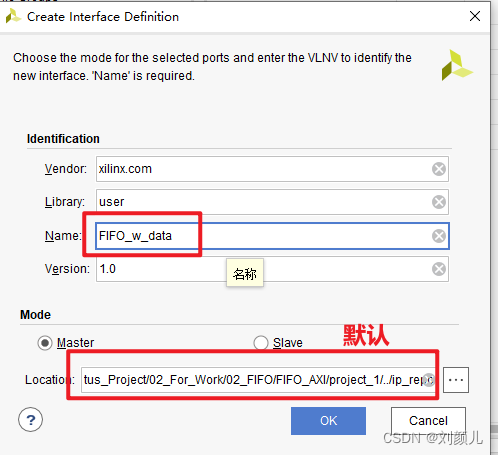

注:下面2张图是举的例子,为后面补充的内容,和上面的地址不同

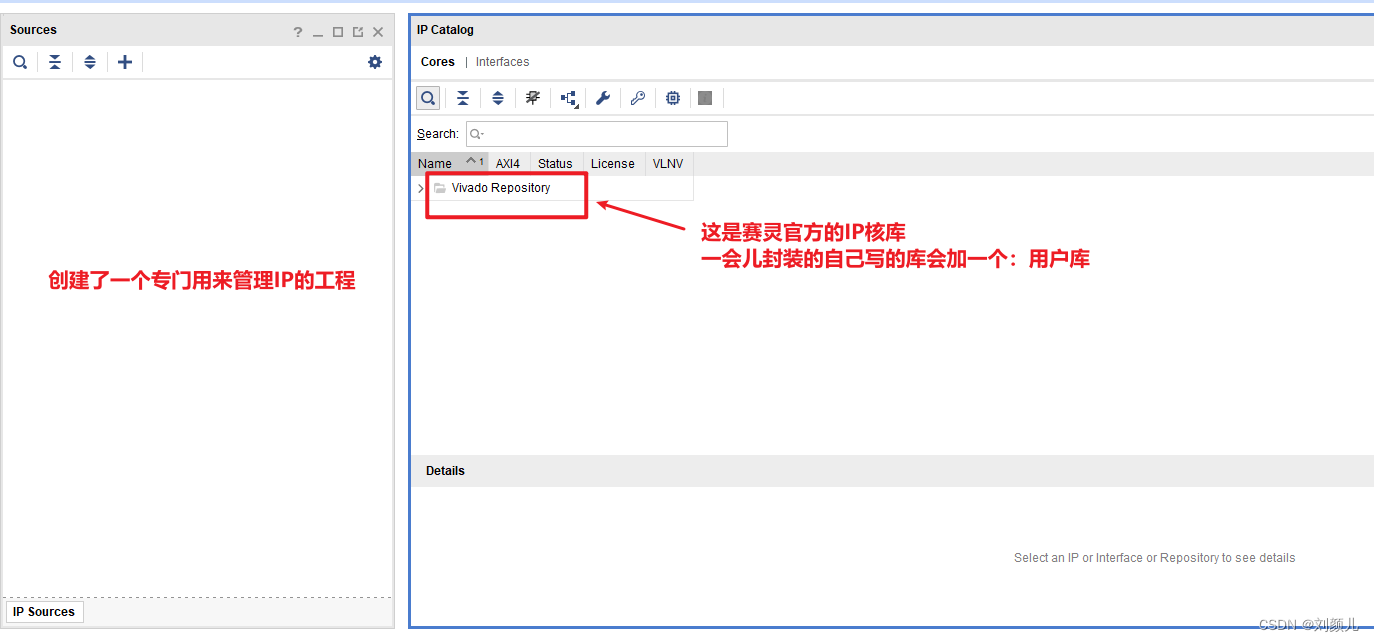

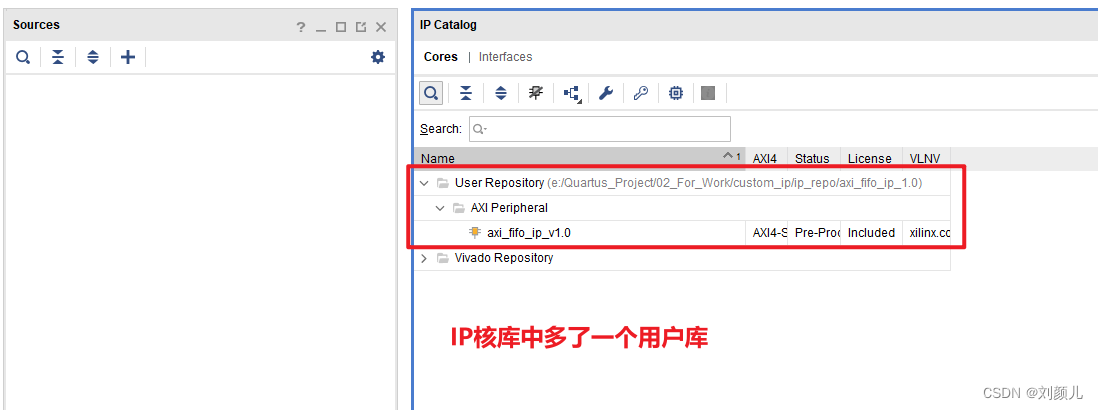

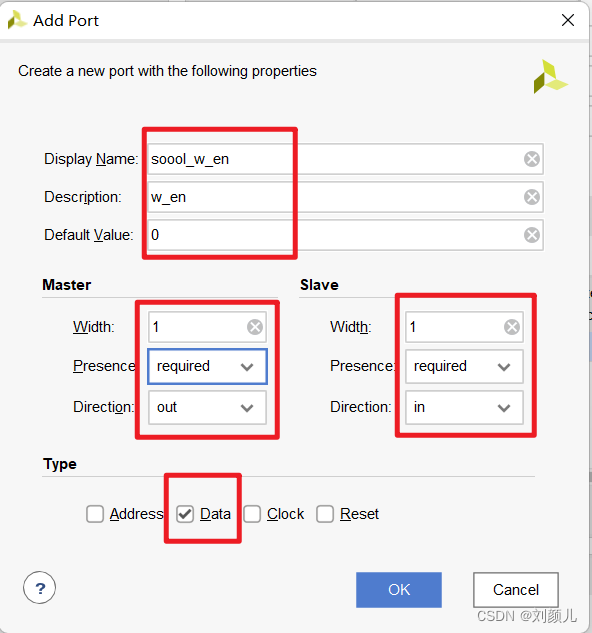

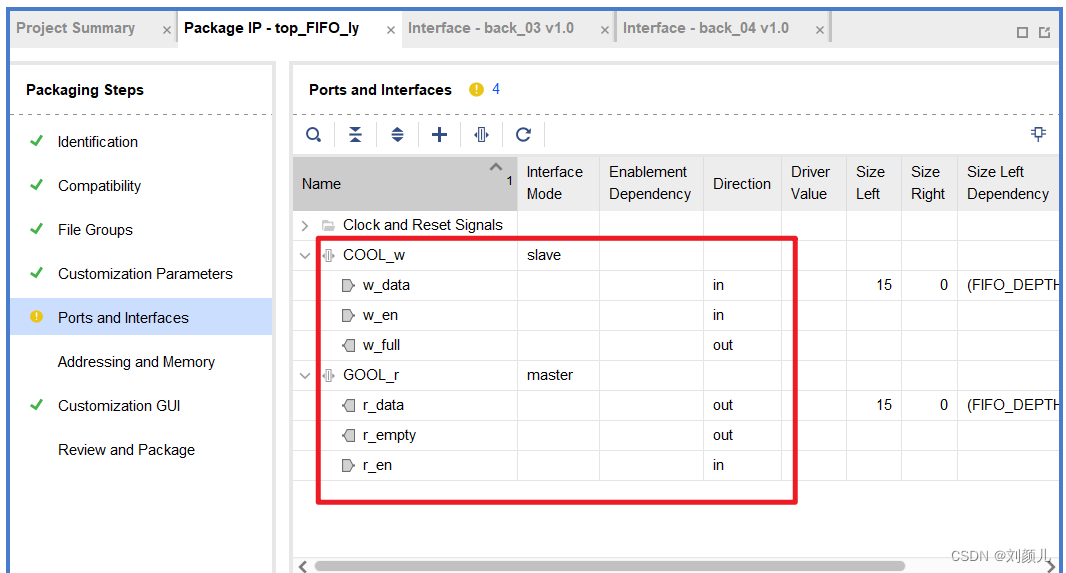

添加完成后,如下图:

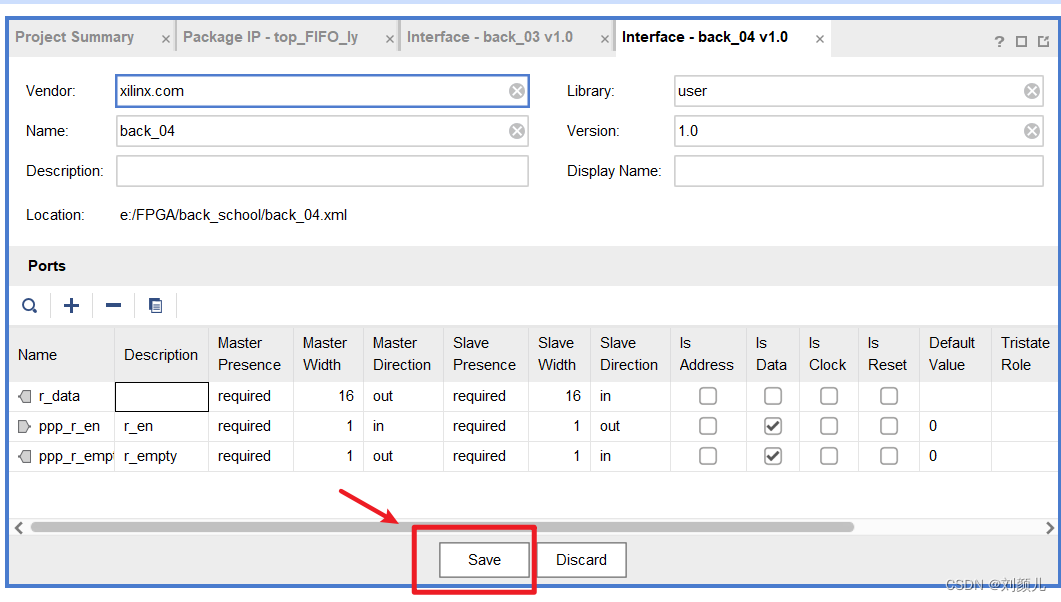

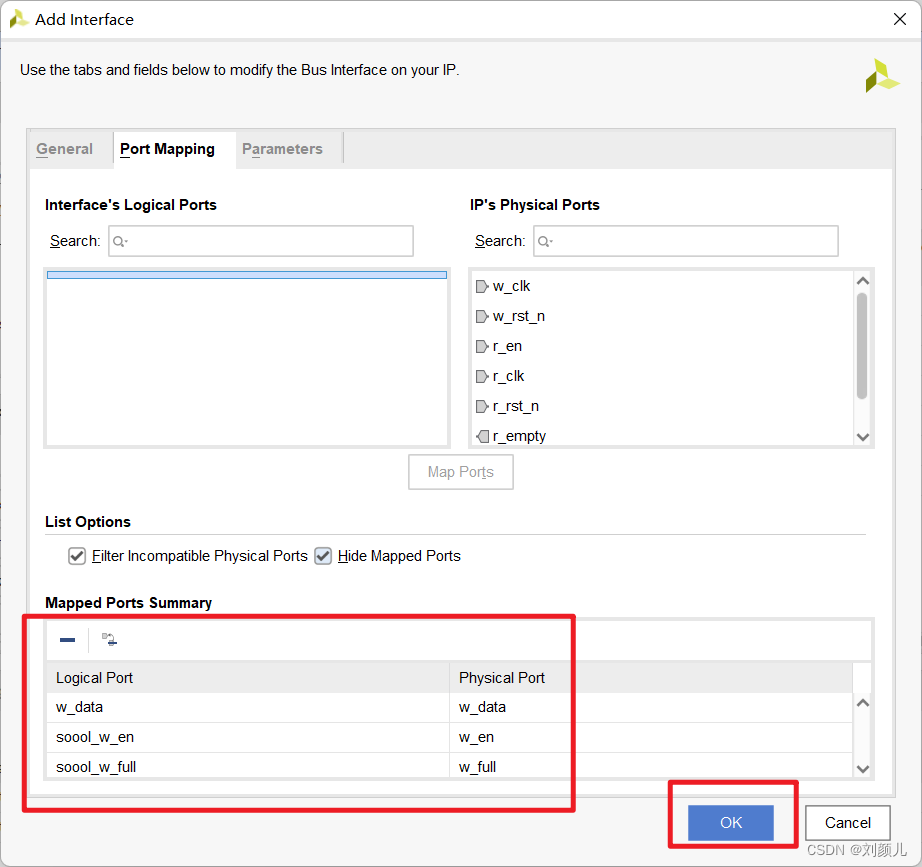

添加完成后,如下图:  按照同样的操作,也将读端口定义完成,并且点击下方的:SAVE

按照同样的操作,也将读端口定义完成,并且点击下方的:SAVE

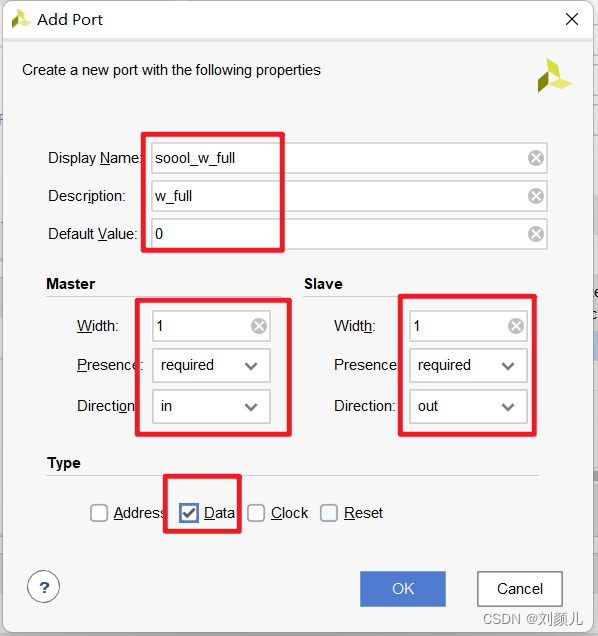

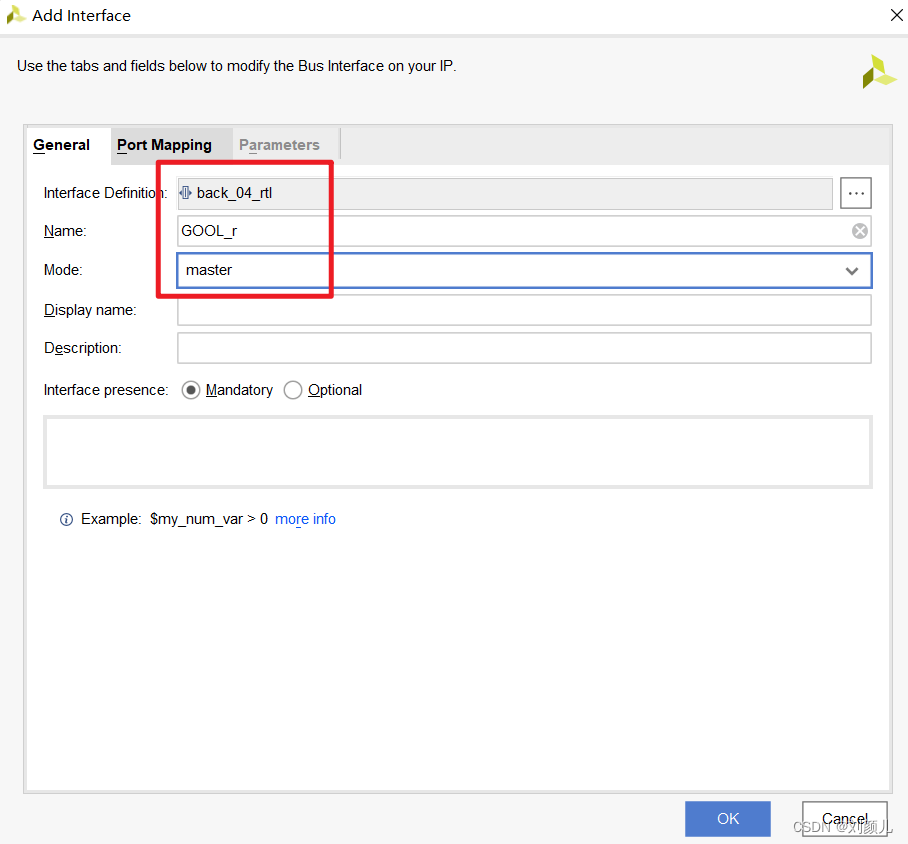

同理,配置读端口

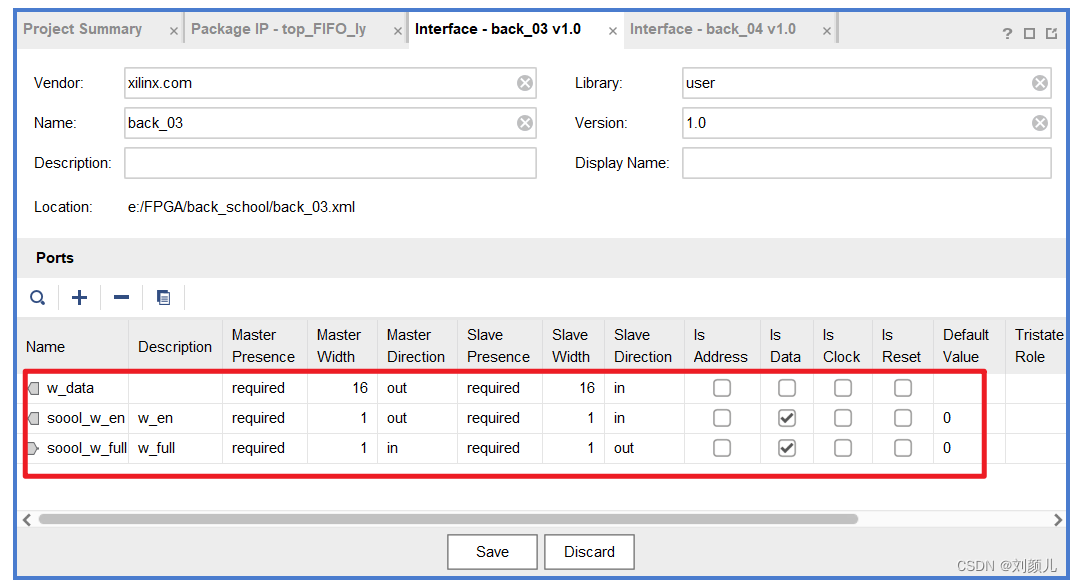

同理,配置读端口  配置完成后,如图

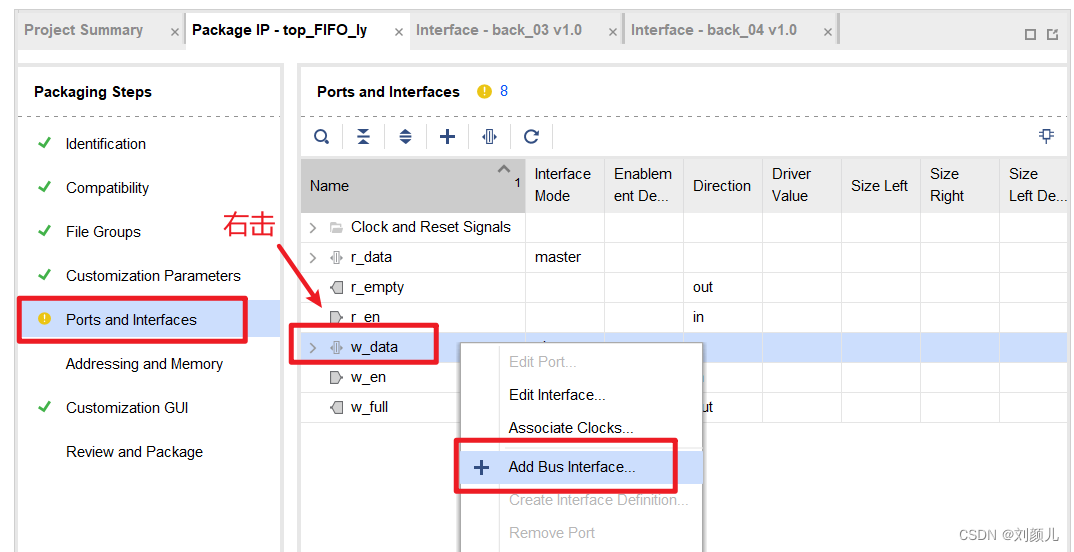

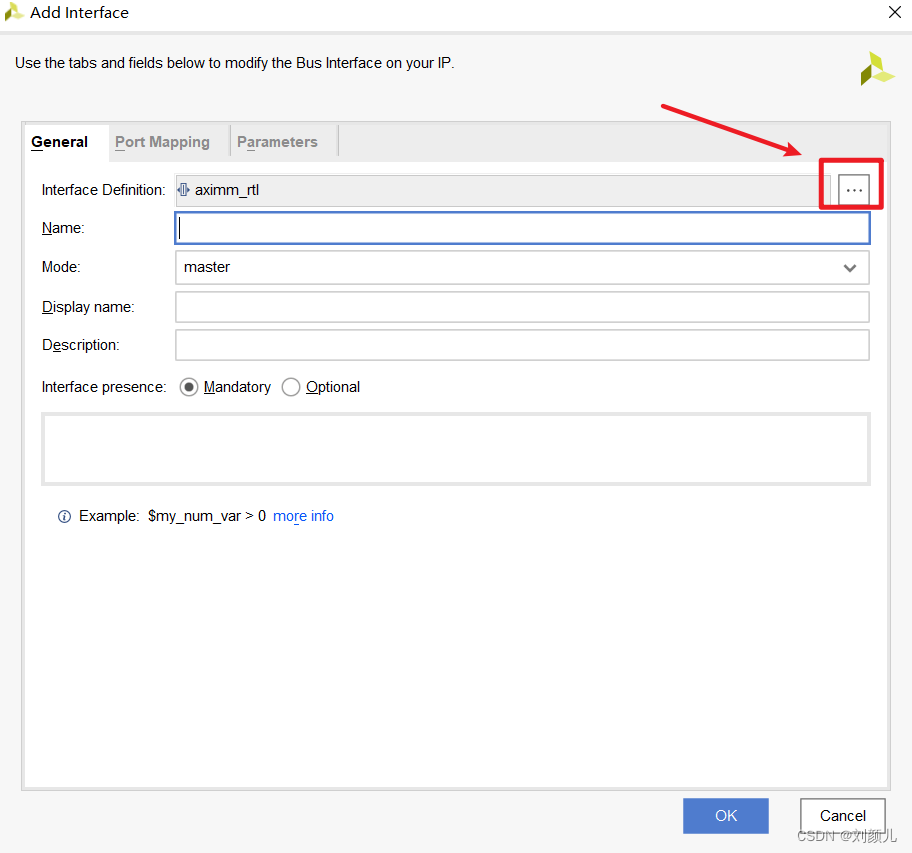

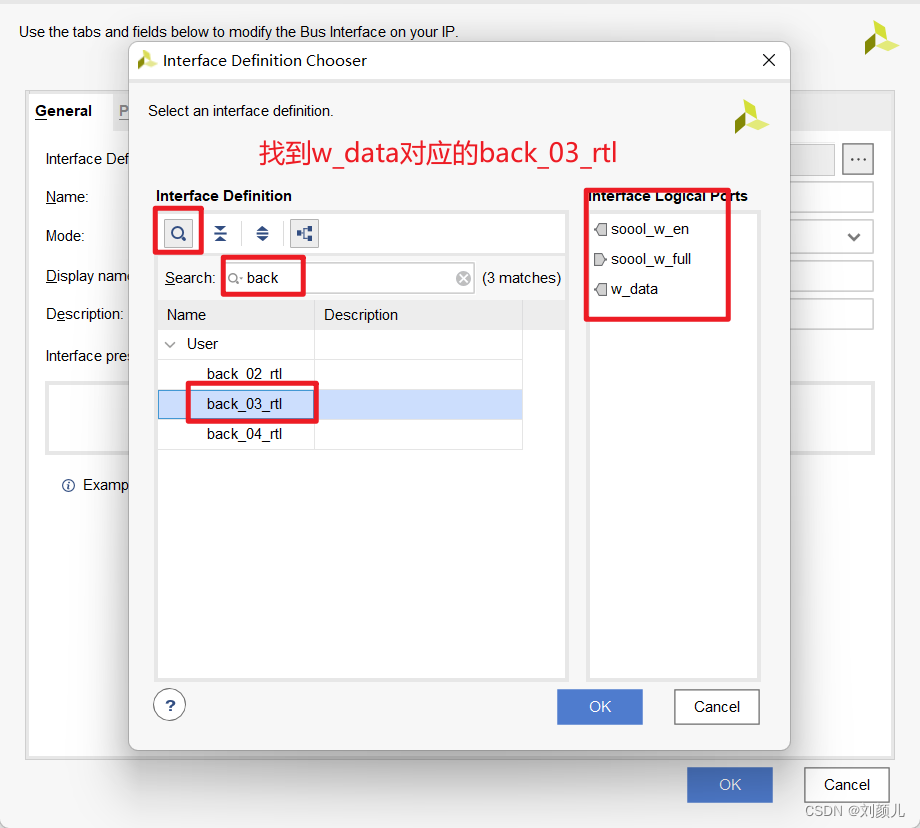

配置完成后,如图

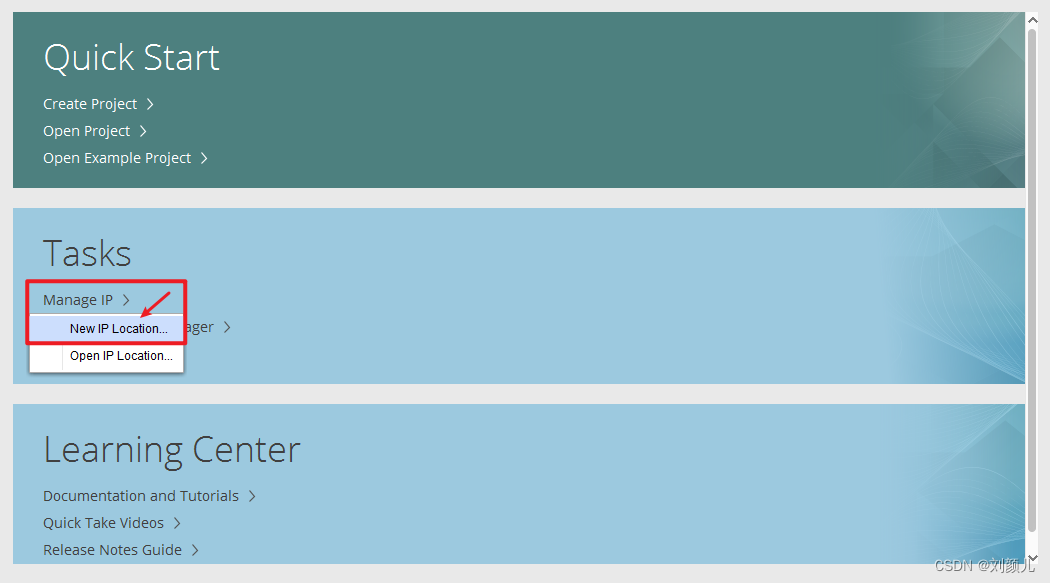

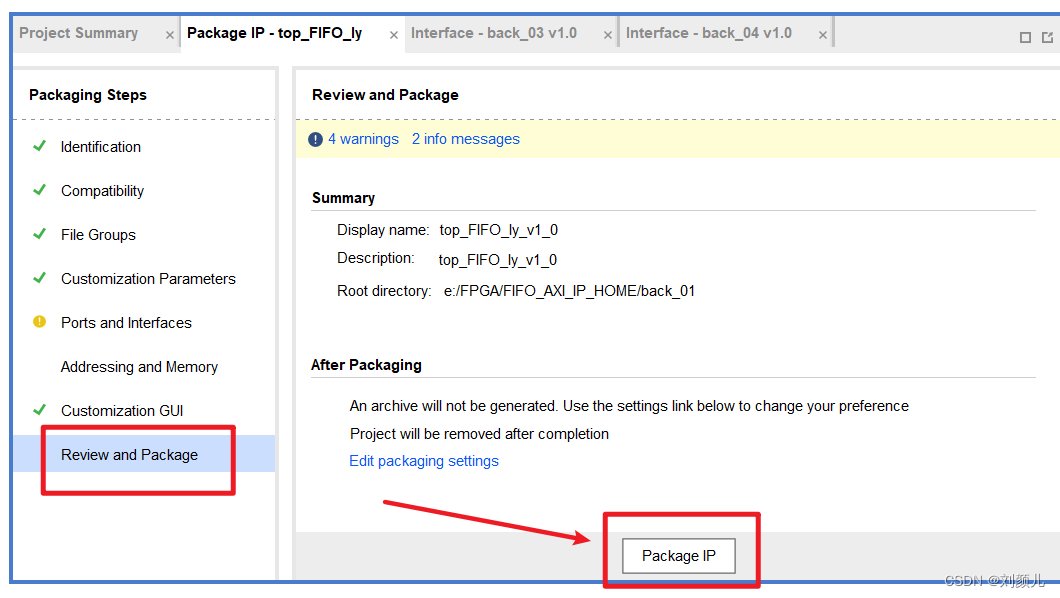

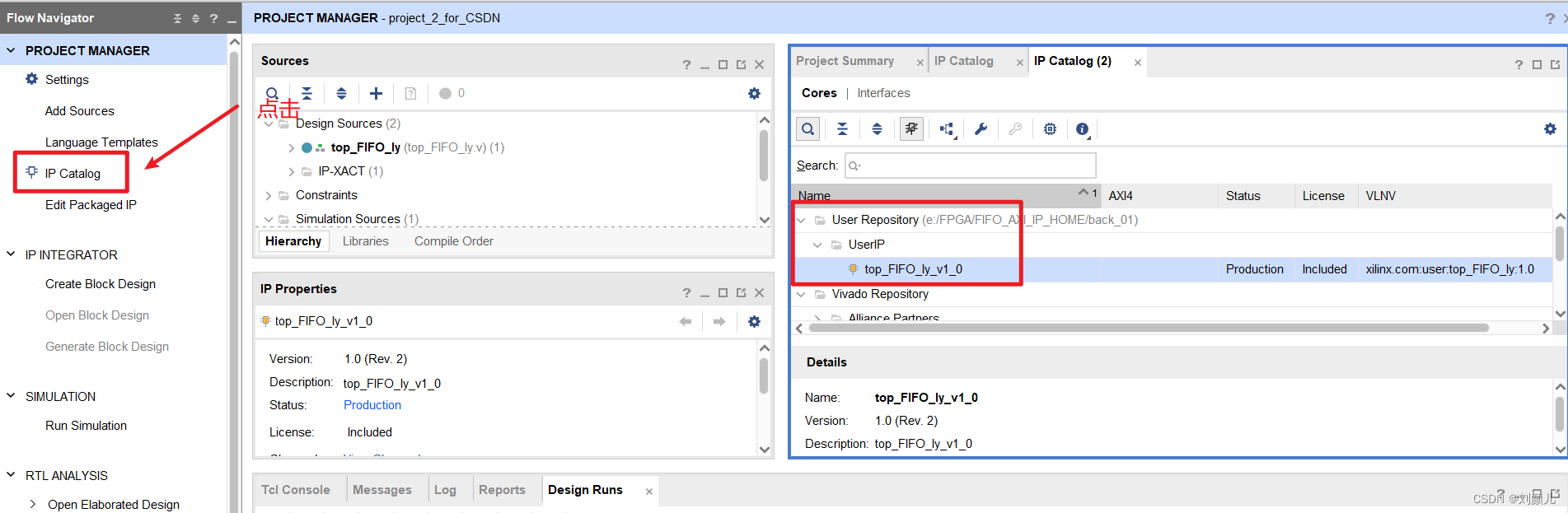

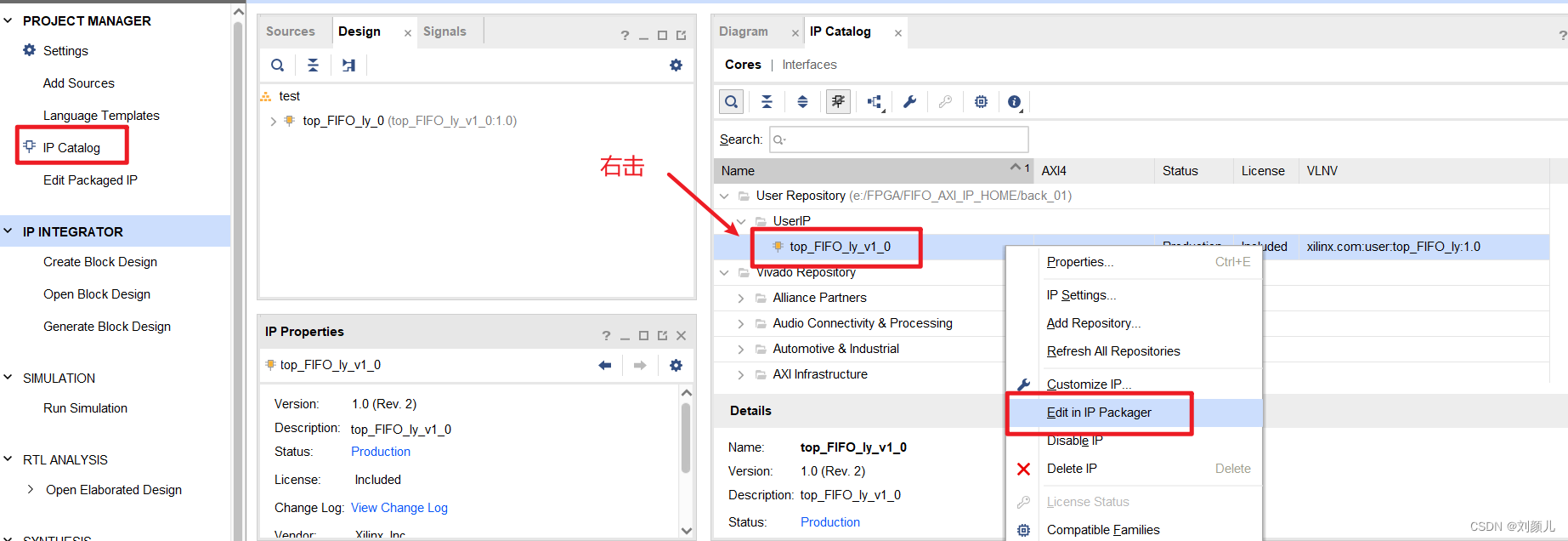

然后返回最初的工程,如图操作即可看到刚刚生成的IP核

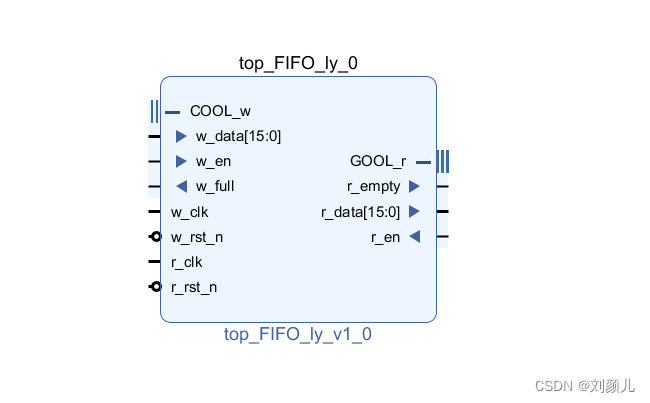

然后返回最初的工程,如图操作即可看到刚刚生成的IP核  创建一个BD图像化文件,然后即可调出刚刚生成的IP核,如图:

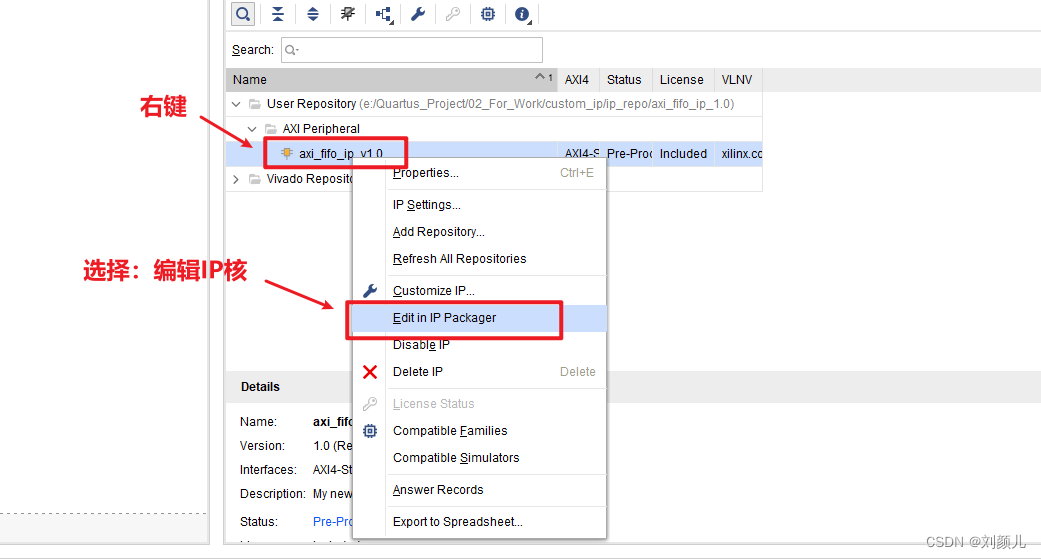

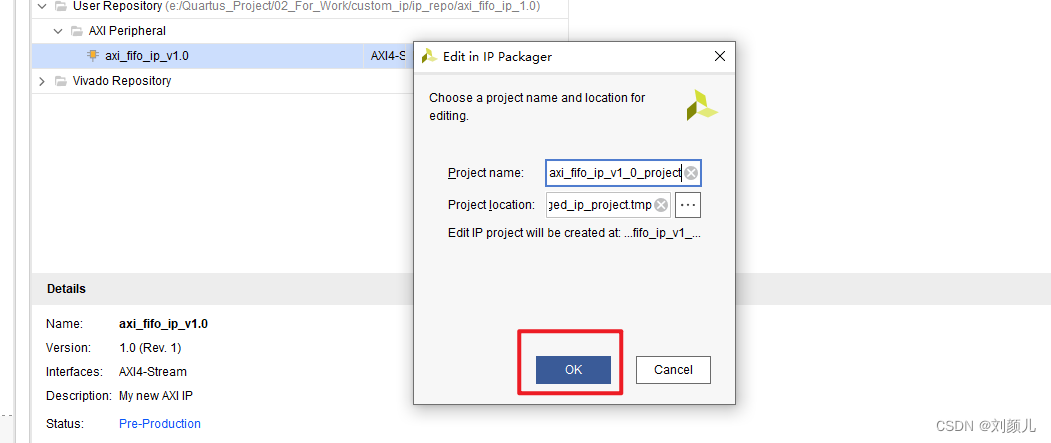

创建一个BD图像化文件,然后即可调出刚刚生成的IP核,如图:  如果想要更改IP核,如图即可打开IP核的工程文件

如果想要更改IP核,如图即可打开IP核的工程文件

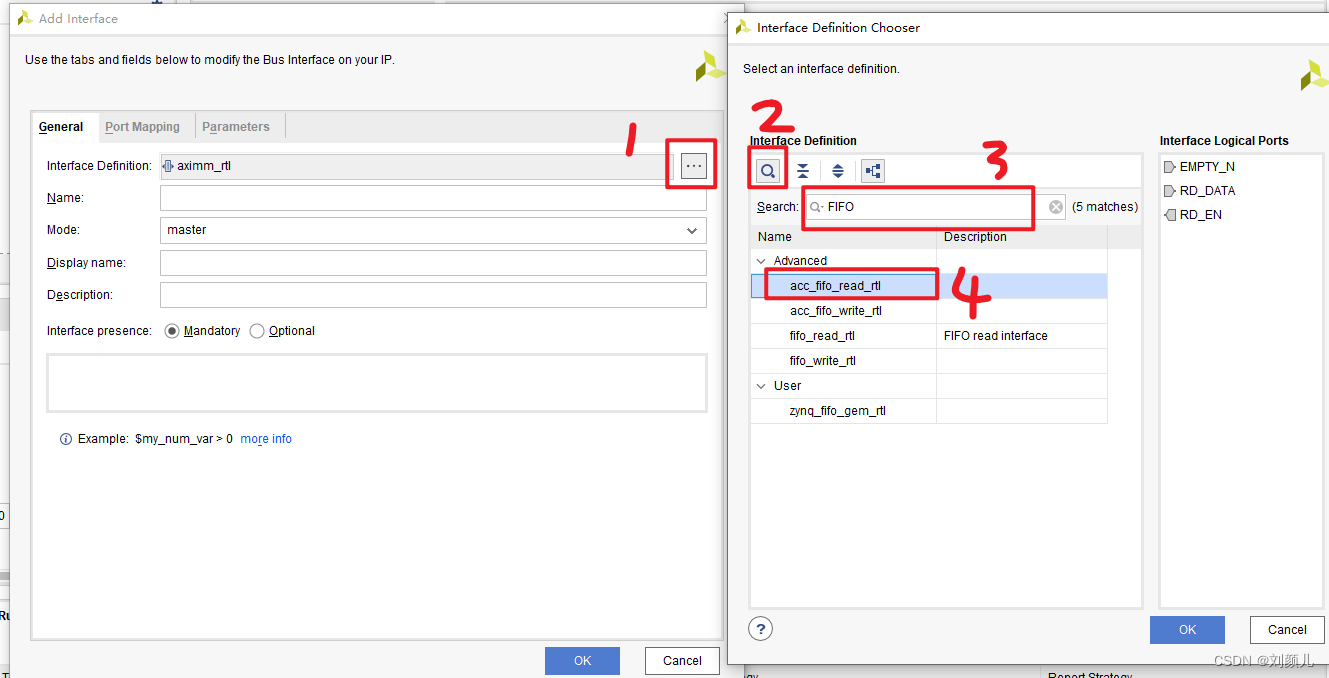

补充:在给FIFO添加AXI端口之前,可以搜索一下看看有没有定义FIFO的端口

如果没有,就需要如上的操作自定义端口

如果没有,就需要如上的操作自定义端口