题目描述

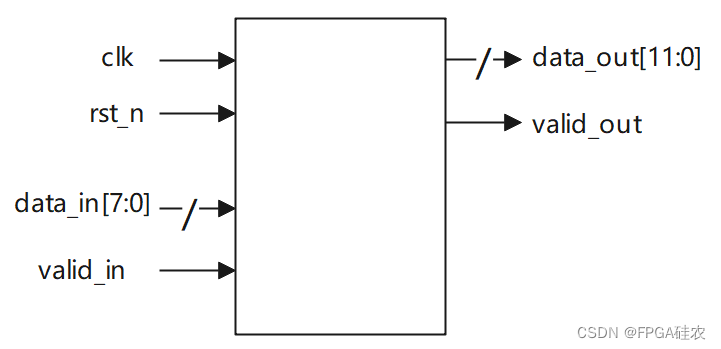

实现数据位宽转换电路,实现8bit数据输入转换为12bit数据输出。其中,先到的数据应置于输出的高bit位。 电路的接口如下图所示。valid_in用来指示数据输入data_in的有效性,valid_out用来指示数据输出data_out的有效性;clk是时钟信号;rst_n是异步复位信号。

`timescale 1ns/1ns

module width_8to12(

input clk ,

input rst_n ,

input valid_in ,

input [7:0] data_in ,

output reg valid_out,

output reg [11:0] data_out

);

//24=8*3=12*2

reg [1:0] data_cnt;

reg [11:0] data_reg;

always@(posedge clk,negedge rst_n)

if(~rst_n)

data_cnt

关注

打赏

最近更新

- 深拷贝和浅拷贝的区别(重点)

- 【Vue】走进Vue框架世界

- 【云服务器】项目部署—搭建网站—vue电商后台管理系统

- 【React介绍】 一文带你深入React

- 【React】React组件实例的三大属性之state,props,refs(你学废了吗)

- 【脚手架VueCLI】从零开始,创建一个VUE项目

- 【React】深入理解React组件生命周期----图文详解(含代码)

- 【React】DOM的Diffing算法是什么?以及DOM中key的作用----经典面试题

- 【React】1_使用React脚手架创建项目步骤--------详解(含项目结构说明)

- 【React】2_如何使用react脚手架写一个简单的页面?