- 1 从MOS管原理学起

-

- 1.1 N沟道增强型MOS管:

- 1.2 其他3种类型MOS管

- 2 CMOS组成的门电路

-

- 2.1 CMOS反相器

-

- 2.1.1 电路结构

- 2.1.2 动态特性

- 2.2 其他CMOS门电路

-

- 2.2.1 CMOS与非门

- 2.2.2 CMOS或非门

- 2.2.3 CMOS传输门

- 2.2.4 三态输出CMOS门电路

- 3 触发器

-

- 3.1 各触发器表达式

- 3.2 SR锁存器

- 3.3 电平触发的触发器

- 3.4 脉冲触发的触发器

- 3.5 边沿触发的触发器

- 3.6 触发器的动态特性

-

- 3.6.1 SR锁存器的动态特性

- 3.6.2 电平触发SR触发器的动态特性

- 3.6.3 主从触发器的动态特性

- 4 亚稳态(metastability)

-

- 4.1 为什么会产生亚稳态?

- 4.2 亚稳态的影响?

- 4.3 为什么同步寄存可以减少亚稳态的概率?

- 4.4 为什么需要多级同步寄存?

- 4.5 亚稳态怎么衡量?

- 4.6 亚稳态怎么降低发生概率

- 要点总结

- 参考资料

- revision

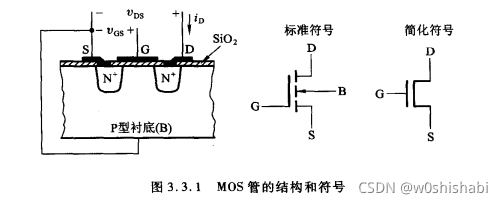

MOS管(Metal-Oxide-Semiconductor Field-Effect Transistor,金属氧化物半导体 场效应晶体管)

1.1 N沟道增强型MOS管:

-

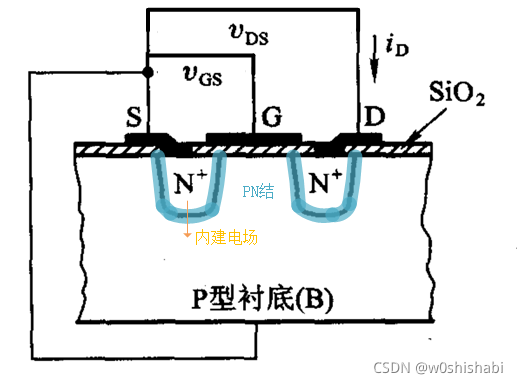

不加电压,此时,载流子由于浓度差而产生的扩散作用 与 内建电场作用下的漂移运动 达到动态平衡,形成PN结。源极S(Source)与漏极D(Drain)之间为两只背向的PN结。不存在导电沟道,所以源漏不导通。

-

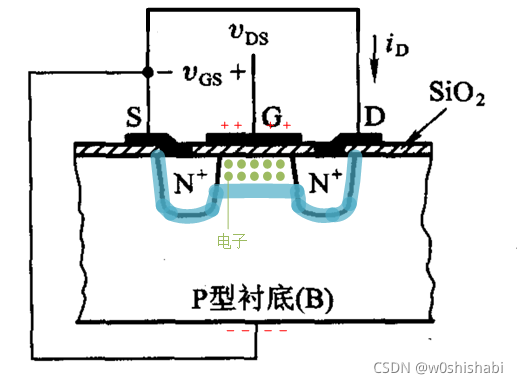

v D S = 0 , v G S > 0 v_{DS}=0,v_{GS}>0 vDS=0,vGS>0。注意栅极G(Gate)与P型衬底间有一层 S i O 2 SiO_2 SiO2,导致不导通,但由于外电场作用吸引电子。这些电子形成N型薄层(反型层)

使沟道刚形成的电压称为开启电压( U

G

S

(

t

h

)

U_{GS(th)} UGS(th)), v

G

S

v_{GS} vGS越大,沟道越大,电阻越小。

3. v

D

S

>

0

,

v

G

S

>

U

G

S

(

t

h

)

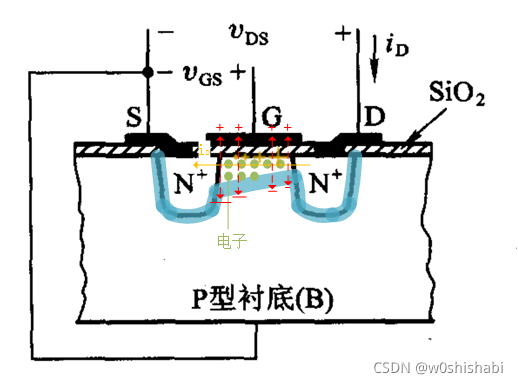

v_{DS}>0,v_{GS}>U_{GS(th)} vDS>0,vGS>UGS(th)。

因为存在沟道,若 v

D

S

>

0

v_{DS}>0 vDS>0,则有漏极到源极的电流。

造成:沟道中各点与栅极间的电压不相等,而是沿沟道从源极到漏极逐渐变大,即漏极一侧的耗尽层比源极宽。即漏极一侧沟道比源极窄:

结果:

-

v

D

S

<

v

G

S

−

U

G

S

(

t

h

)

v_{DS}

关注打赏

最近更新

- 深拷贝和浅拷贝的区别(重点)

- 【Vue】走进Vue框架世界

- 【云服务器】项目部署—搭建网站—vue电商后台管理系统

- 【React介绍】 一文带你深入React

- 【React】React组件实例的三大属性之state,props,refs(你学废了吗)

- 【脚手架VueCLI】从零开始,创建一个VUE项目

- 【React】深入理解React组件生命周期----图文详解(含代码)

- 【React】DOM的Diffing算法是什么?以及DOM中key的作用----经典面试题

- 【React】1_使用React脚手架创建项目步骤--------详解(含项目结构说明)

- 【React】2_如何使用react脚手架写一个简单的页面?