以下内容参考自:《正点原子逻辑设计指南》

逻辑设计中一般存在多个时钟,那么信号在多个时钟之间如何切换呢?这个就涉及到了异步电路设计,异步电路设计也是逻辑设计中非常重要的设计,可以说异步处理不好,逻辑出问题的可能性非常大。

一、亚稳态简介在介绍异步设计方法之前,我们先了解下亚稳定的概念,为什么要先了解亚稳态呢?因为异步电路如果直接使用寄存器采样会出现问题,最常见的就是出现亚稳态。寄存器采样需要满足一定的建立时间(setup)和保持时间(holdup),而异步电路没有办法保证建立时间(setup)和保持时间(holdup),所以会出现亚稳态。

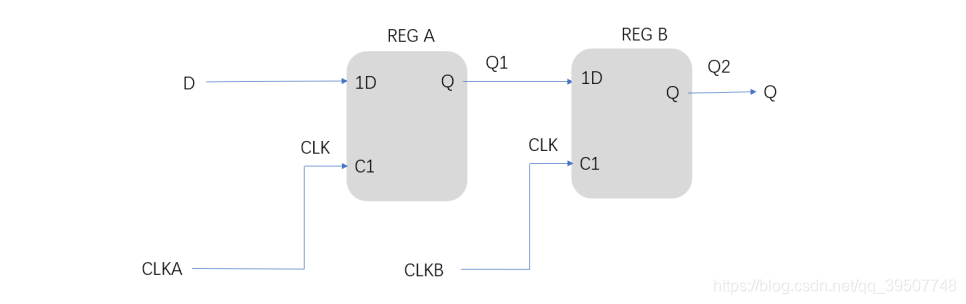

下图为两个不同时钟的寄存器的示意图,寄存器 B 采样可能采样到寄存器 A 输出的任意状态,包括 Q 的信号跳变沿。

但是寄存器的 D 端信号需要满足建立时间 Tsu 和保持时间 Th 要求,否则就会出现 Q 端采样到不确定的值的状态,就是俗称的亚稳态。

但是寄存器的 D 端信号需要满足建立时间 Tsu 和保持时间 Th 要求,否则就会出现 Q 端采样到不确定的值的状态,就是俗称的亚稳态。